Tool/software:

Hello,

We are doing analysis and validation of our new board tat features two ADS54J60 and we are noticing lots of noise at higher levels than expected.

For context we have applied SMA shorts to channels, 50 ohm terminations, and even directly shorting the ADC inputs.

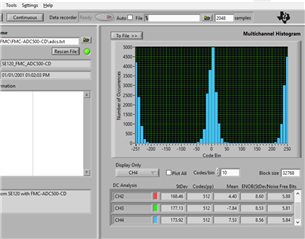

We have the following histogram from the ADC Pro tool showing channel 4 which has a direct short on the ADC inputs:

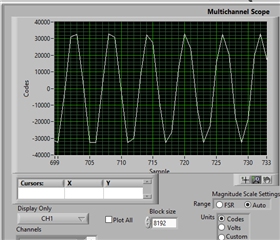

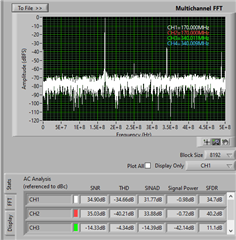

I am also including a capture file (adcs.txt) where, channel 1 is floating (no termination or short on this channel), channel 2 has a 50 ohm termination, channel 3 has a short on the connector and channel 4 has a short directly on the ADC inputs.

Can we get some suggestions of where this noise is potentially coming from?

Thanks,

Ryan