Other Parts Discussed in Thread: CDCE6214, LMK03318

Tool/software:

Hello,

I am studying a new design with DAC38RF85 chip (or other reference from the DAC38RF8x family).

The frequency reference of this design must be 10 MHz. This frequency is too low for the reference input of the DAC38RF85 (100 MHz min).

Thus, I am looking for a clock generator which will be able to generate a 100 MHz clock from the 10 MHz reference.

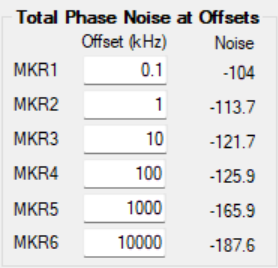

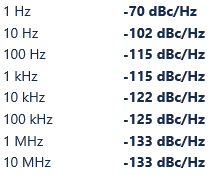

The phase noise at the output of the clock generator must comply with the following requirements (max values) :

The aim is to get a cheap clock generator (< 5 $ for 500p) in a small package and with a low power consumption.

Since this clock generator will drive the DAC38RF8x part, one output shall be directly compatible. Another output (differential) will be required in order to supply the same 100 MHz reference to the processing part (output format to be defined).

What reference do you recommend for this kind of operation ?

Thanks for your help.

Regards,

Alain