Tool/software:

Hi team, I have some questions regarding the ADS114S08:

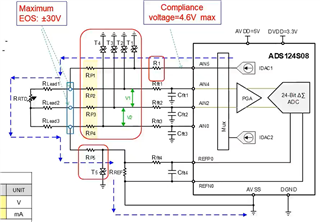

Filter design (based on this app note):

1. In example 3.1, I want to confirm my understanding of the filter design / requirements. The anti-aliasing is handled by the internal decimation filter with a cutoff around 3.5 Hz, so your external filter is used for attenuating external noise on the RTD lines. Where did the ~250 Hz frequency cutoff to achieve this come from?

2. As the part multiplexes through multiple inputs (ie IDAC chopping, measuring REFP0, REFN0), the effective sample rate will decrease because you're not measuring every input at an interval of 20Hz, how do I be sure that there's effective anti-aliasing in this case?

3. How are idle tones accounted for in this design / what parameters on the data sheet reflect this performance, as this will be likely measuring a near-DC voltage?

4. Many of the references I've seen for this part show the REFN pin have a filter where one end is grounded. Is there any advantage to this versus just grounding the pin directly and using a single ended filter for REFP?

Input protection (based on this app note):

1. Is there a reason the input / output nets are protected twice, one for each pin? I assume it's to maintain a kelvin style connection right to the connector. Would there be a significant downside to using one resistor and diode near the connector and using a kelvin connection to there?

General:

1. Is there any advantage to using an external clock with one or multiple parts?

Thanks in advance for taking the time to answer these questions. Please let me know if we could set up a design review as well.

Best,

Nick