Tool/software:

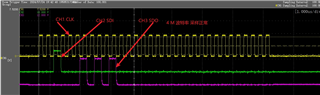

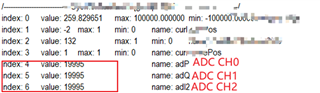

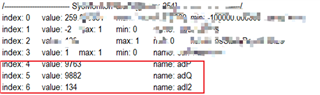

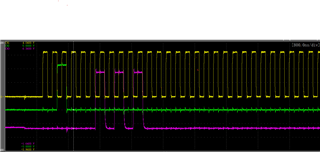

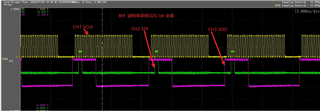

I have met a TLV2548CPW SPI boud rate issue , when I use SPI boud rate of 8M and read a channel with 40 periods , the AIN0-AIN2 digital output are all high level and result is wrong ,I have got a failure rate of 40 persents(8 out of 20), but when I decrease boud rate to 4M and the result is correct , I checked SCLK/SDI/SDO signal , they all looks great .see below Oscilloscope snapshoot , Could you please help to check why the chip cannot support 8M boud rate with the sample rate is200 kbps(=1*8M/40=200K/s) while OK to 4M boud rate? the datasheet does specified the sample rate to be 200kbps.

8 M SPI boudrate:

4M SPI boud rate: