Tool/software:

Dear Community,

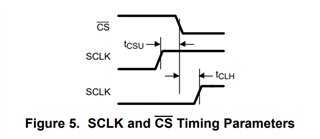

While analyzing the serial timing diagram in the datasheet, I’m unable to determine the values of CPOL and CPHA. Could you please clarify what they are? Additionally, on page 5 (note 2), it states: "Clock may be either high or low when CS is asserted as long as setup and hold times tCSU and tCLH are strictly observed." Does this mean I can use two different values for CPOL?

Thank you.