Tool/software:

hello,

I under stand that the LMK can accept on clkin1 in pin in distribution mode up to 3Ghz.

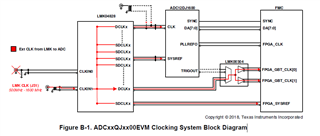

I wish to design a system according the below diagram (Figure B-1. ADCxxQJxx00EVM Clocking System Block Diagram FROM SLAU808.pdf)

- Input clock to clkin1 of the LMK is 1Ghz.

- DCLK out to the ADC clk in also 1Ghz = sample rate

- ADC in JMODE8 = 4 lanes/ 12bit/64/66 = lane rate of 12.375Gbps

- According to ADC Data Sheet Trig Out will be 386.71875MHz (Lane rate/32 or could be /64) used optionally to FPGA GBT clock.

- Given all the above I need to know what is the frequency LMK generates on the output going to FPGA GBT clock?

Regards,

Giora