Tool/software:

Hello,I build a ads1299 record system.

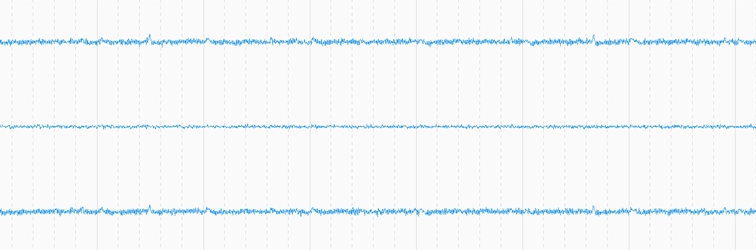

When the same group of ADS1299 samples at 4K and below, the input noise appears to be close to the chip specifications ( under 3uVpp, folled figure) . And I input the tested sine wave, the adc output signal display as expected.

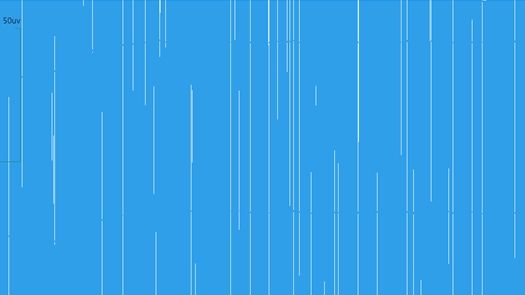

But when I set ADS1299 sample rate at 8KSps and 16KSps, the input noise appears to very large which exceed the display range ( about 1-3 mVpp). Followed figure shows that noise display full screen in input noise case.

The FPGA use one group SPI to write and read 5 pcs ADS1299 in parallel mode. The sclk is 20MHz.