Part Number: ADS114S08B

Tool/software:

Hi,

I am currently designing a multi-channel heating system that will utilize an FPGA to interface with multiple ADS114S08B devices for 4-wire RTD measurements. To optimize the number of FPGA signal lines, I plan to use a single SPI Bus to connect multiple ADS114S08B devices. I have a few questions regarding this setup:

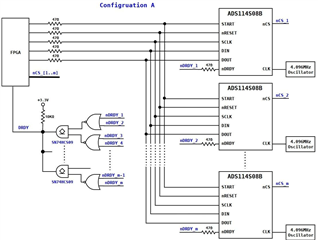

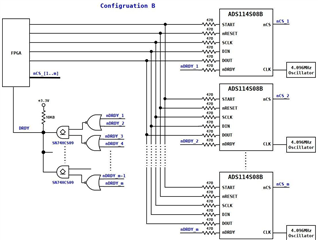

1. The datasheet (section 10.1.1) suggests placing a 47-ohm resistor in series with the digital input and output signals. Between the two resistor configurations shown in the attached diagram, which one is more suitable? Or is there a better connection method you would recommend?

2. What is the maximum number of ADS114S08B devices that can be connected in parallel on the same SPI Bus?

3. Does the choice of using an internal versus an external 4.096MHz clock signal affect the accuracy of the RTD resistance values obtained?

4. In the attached diagram, the DRDY signal is connected such that after the FPGA sends the START/SYNC signal, can we ensure that all ADS114S08B devices have completed conversion and are ready for data readout simply by checking if DRDY = 1?

Thank you for your assistance.

Best regards,