Other Parts Discussed in Thread: OPA388

Tool/software:

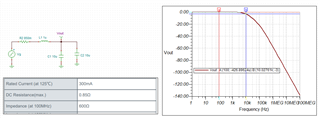

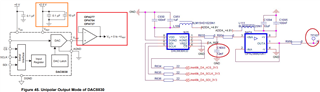

I have chosen the DAC8830 to realize the output of analog signals ranging from 200Hz to 48kHz. The sampling rate is 153.6kHz. The circuit is designed according to the circuit diagram provided in the official website's document TIDA01402. The actual circuit is shown in the following figure.

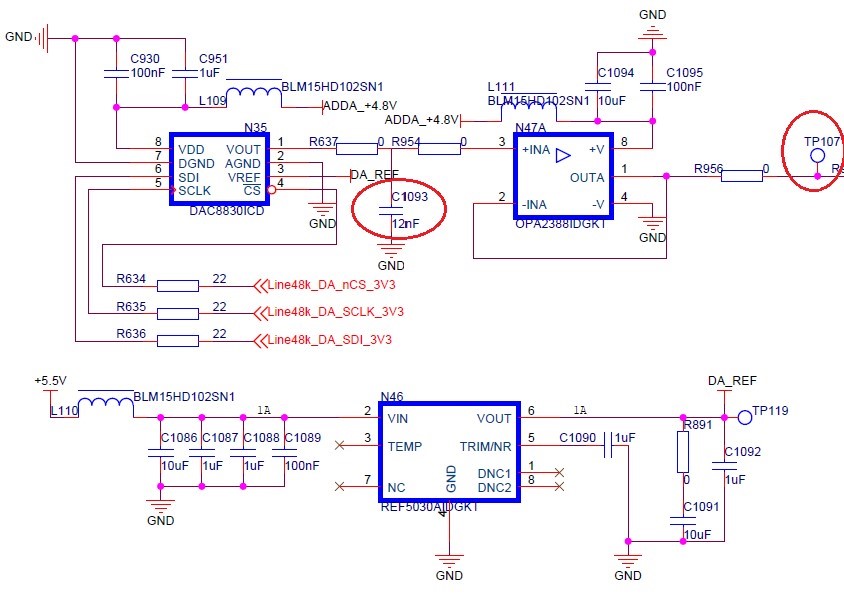

When testing the circuit, I use the IP core on the FPGA platform to generate a sinusoidal digital sequence having a frequency of 1 kHz and an amplitude of 1 Vrms. This signal is then sent to the DAC8830. I measure the analog signal at test point TP107 (with the latter stage circuit disconnected). The measured output signal spectrum is shown in the following figure. The noise floor is basically below -100 dBV. The signal quality is acceptable.

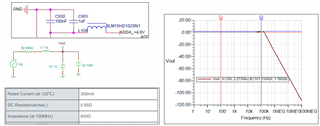

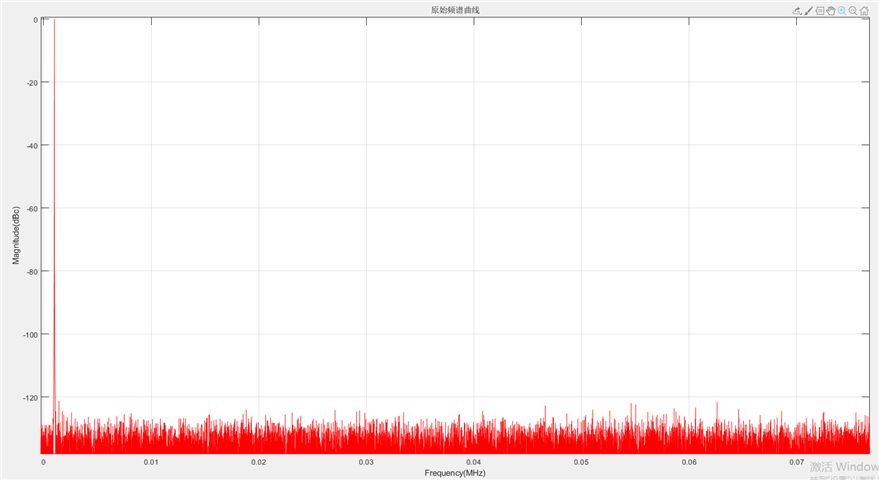

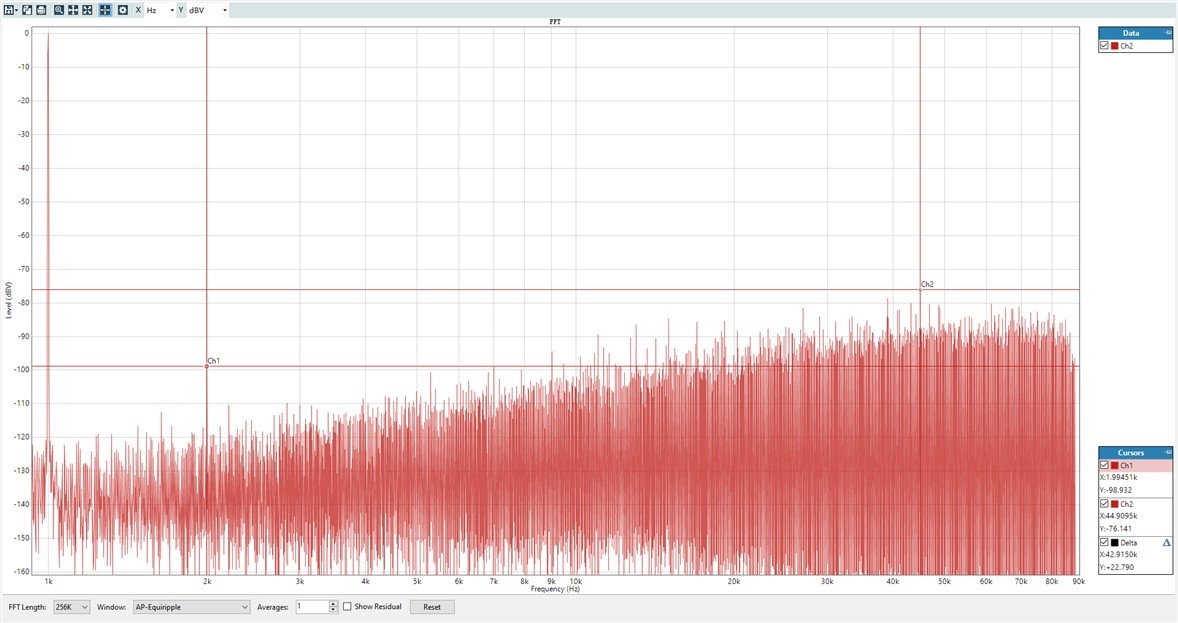

However, since the signal bandwidth reaches 48 kHz, the capacitance value of C1093 in the circuit must be adjusted. In the circuit of TIDA01402 document, a capacitance value of 12 nF is selected. According to the output impedance of 6.25 kΩ given in the DAC8830 datasheet, the cut-off frequency should be about 2.1 kHz, which cannot meet the usage requirements. Changing the capacitance value of C1093 to 340 pF results in a cut-off frequency of about 75 kHz. After changing the capacitance value, a sinusoidal digital sequence having a frequency of 1 kHz and an amplitude of 1 Vrms is still used as the test signal. The signal spectrum measured at TP107 is shown as follows. As the frequency increases, the noise floor also rises. The highest noise floor within the Nyquist frequency reaches 80 dBV. This is rather different from the noise specification of 10 nV/√Hz as described in the datasheet.

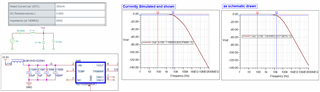

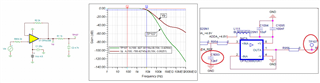

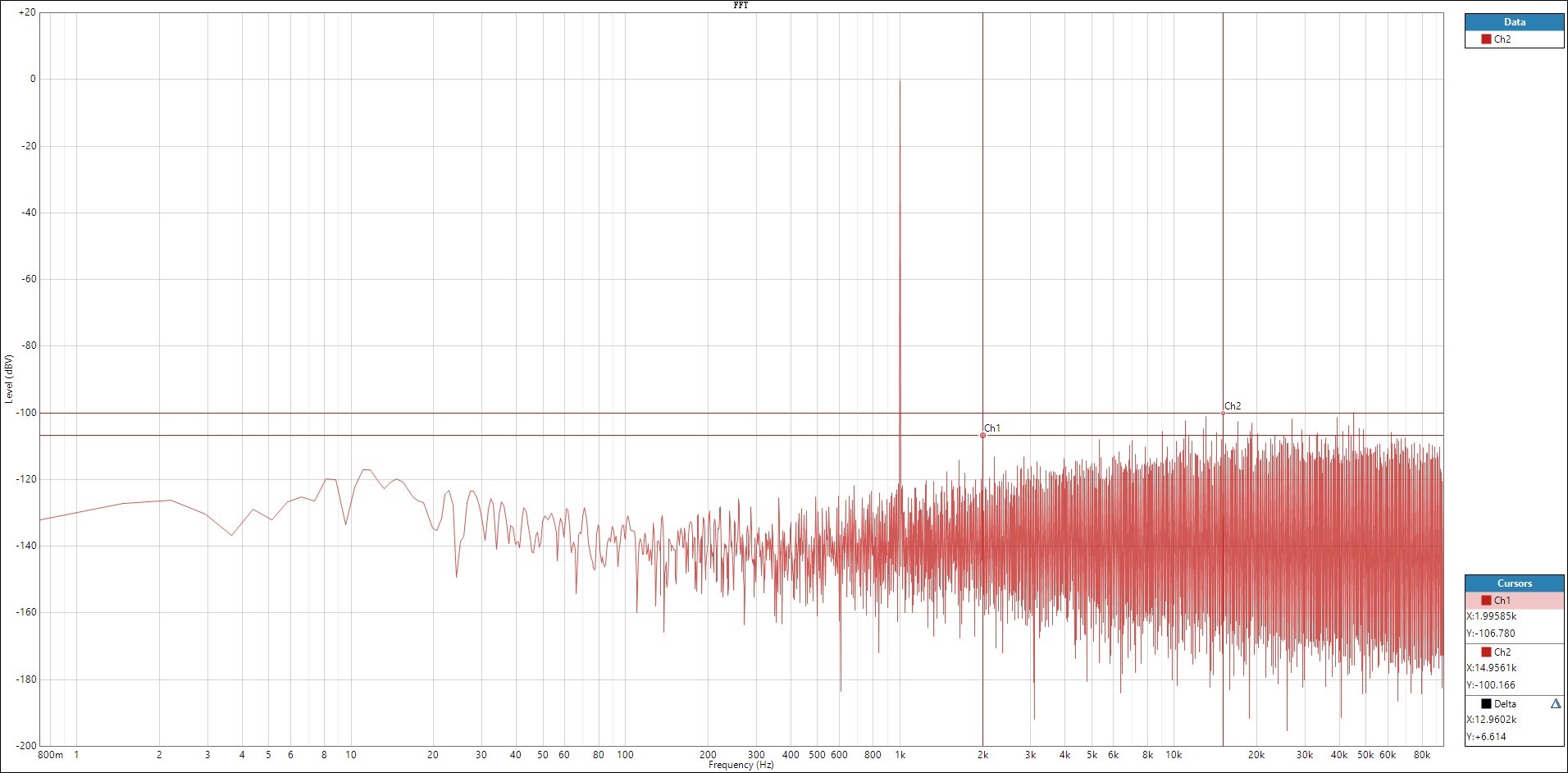

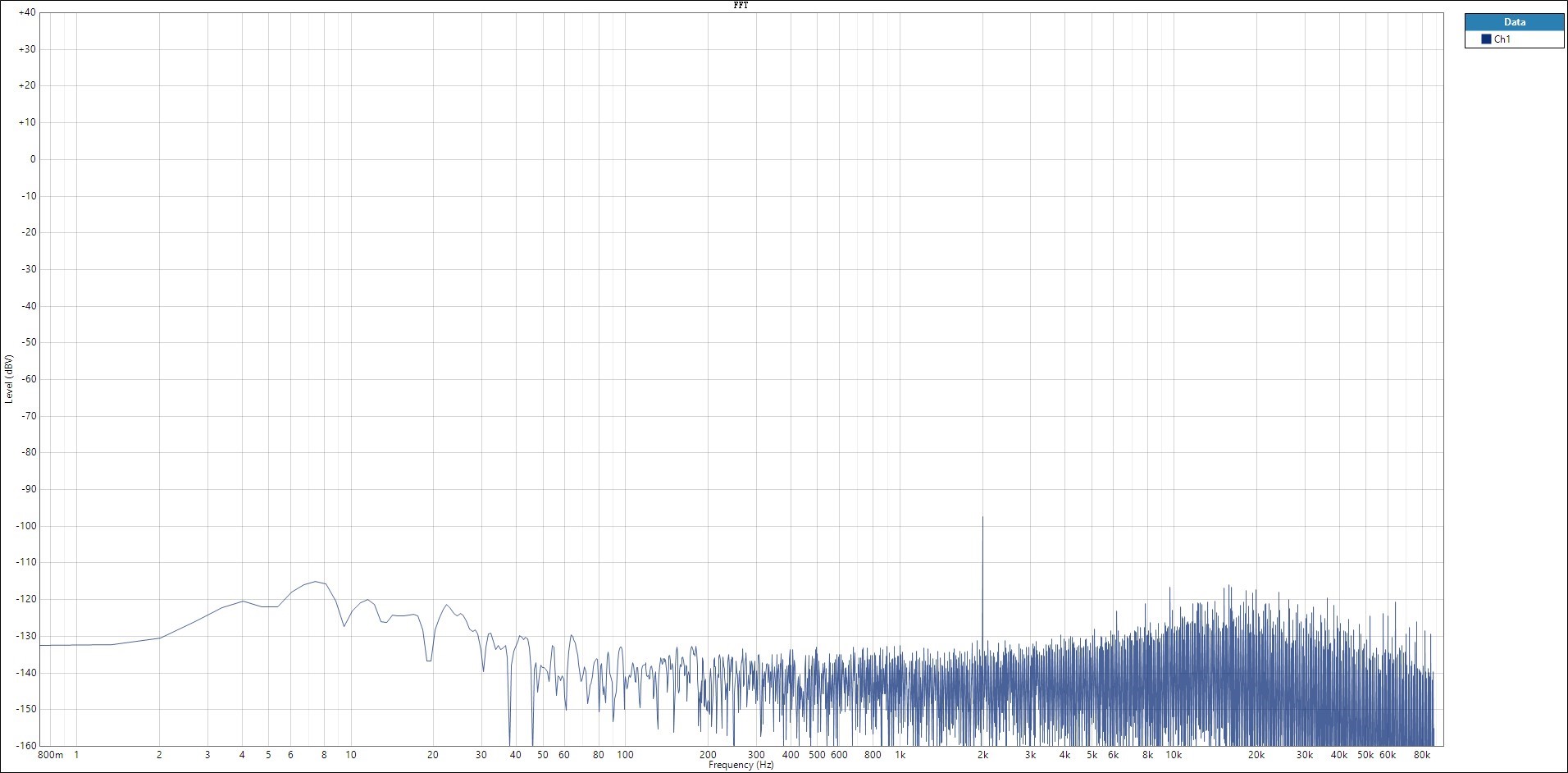

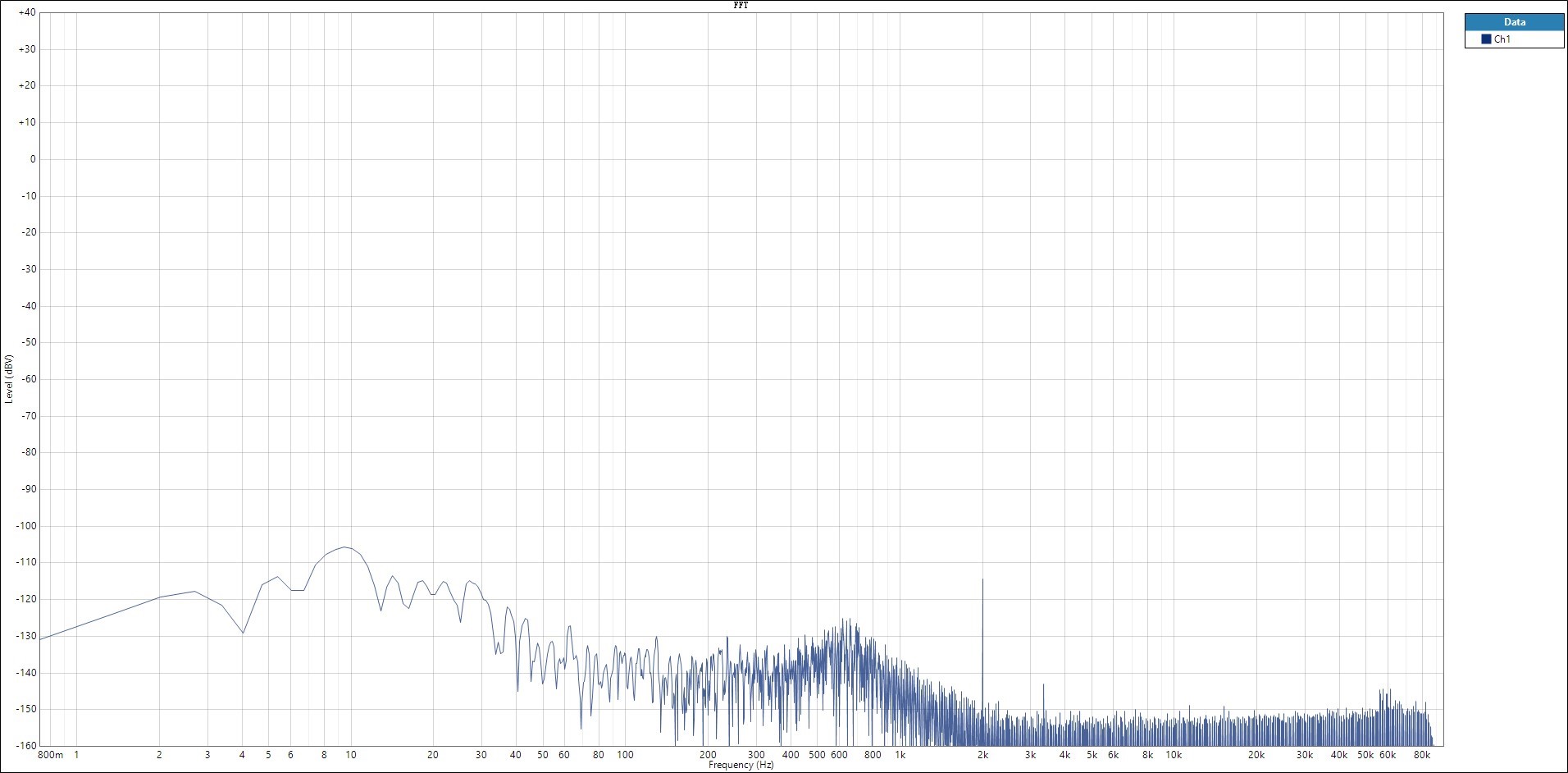

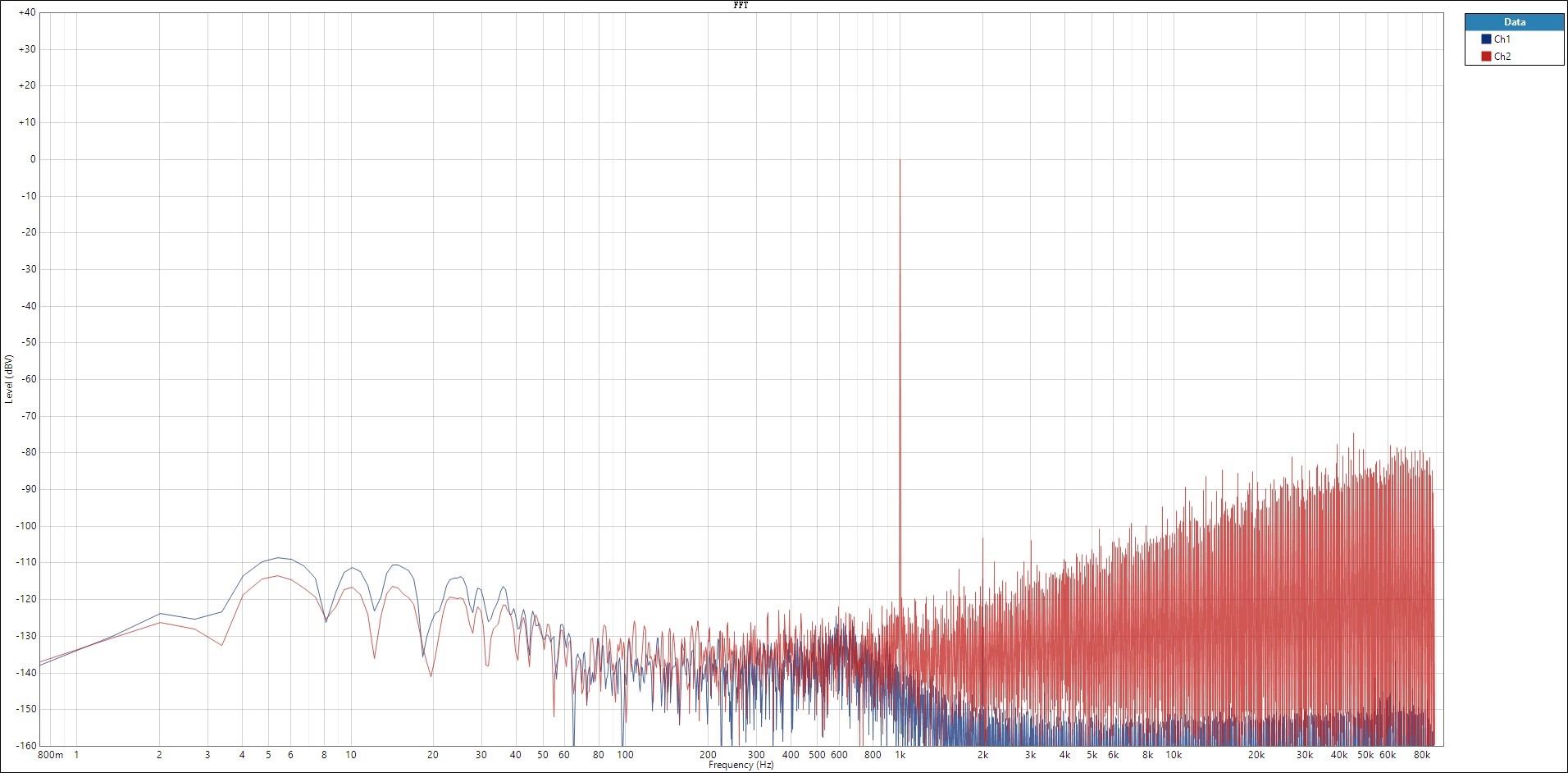

I had suspected that the signal noise might be related to the noise of the reference voltage or power supply. So, I attempted to add filtering treatment to the VREF pin of the DAC8830. However, I discovered that even after reducing the noise on this pin, there was no improvement in the noise of the output signal, as shown in the following figures. Similar tests were performed on the VDD pin, and the results were similar.

Figure:Noise level of VREF pin before adding filtering

Figure:Noise level of VREF pin after adding filtering

Figure:The optimization of noise on the VREF pin has no effect on signal noise

This noise floor level is definitely not what the DAC8830 is supposed to be. Hence, I'd like to post a query to seek advice on what might be the cause for the degradation of the noise level.

Besides,If there are relevant literatures, I would greatly appreciate recommendations.

Thanks,

Howie