Other Parts Discussed in Thread: AMC131M01

Tool/software:

Hi team

In my design a use 9 AMC131M0x (I have 1 - 3 channels per chip) 8 chips run more or less well but 1 AMC131M02 has frequently (about 90% of reading) the SEC_fail Bit set in the status of chip. On the same SPI (shared with individual CS) I have 4 other AMC chips which don't have any problem. All these AMC chips on the same SPI bus has 100% equal setting. I tried follow things:

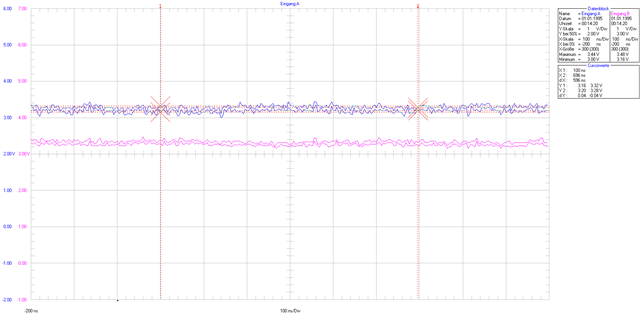

- different CKIN frequencies Result: 7.8MHz around 90% error rate, 4.76MHz around 85% error rate

- different SPI speed: Testet from 3.1MHz - 12.5MHz: result no difference

- I add additional capacitors on primary and secondary side according data sheet application in 1206 housings --> no difference

- I add 1k load to SPI CLK, SPI MOSI and SPI MISO. no difference

- different parameters DCDC_Freq: Best result with default value 0000. If reduce the frequency I in increase the number of fails und under around 3MHz there are only errors

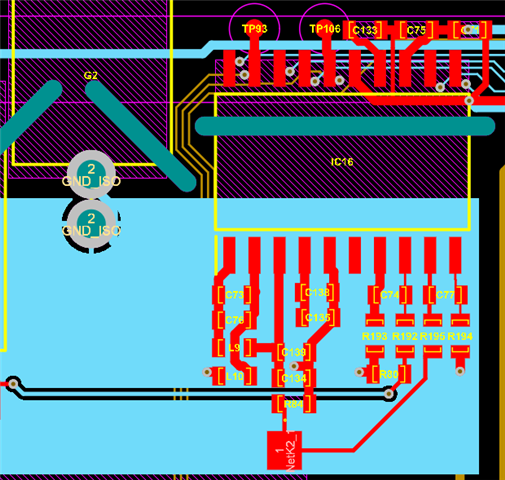

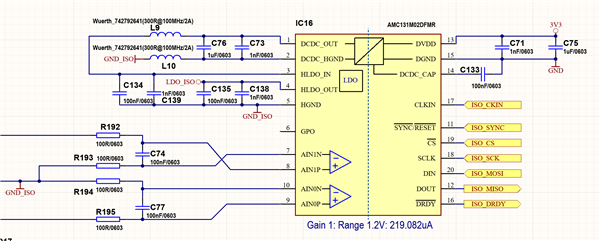

Schematic of AMC131M02 with problems

Initialization at power up:

MODE_ADDRESS: (MODE_DEFAULT & ~(MODE_RX_CRC_EN_MASK | MODE_RESET_MASK)) | MODE_RX_CRC_EN_ENABLED | MODE_RESET_NO_RESET

CLOCK_ADDRESS: (CLOCK_DEFAULT_2CH & ~CLOCK_OSR_MASK) | CLOCK_OSR_2048

DCDC_CTRL_ADDRESS: DCDC_CTRL_DEFAULT

GAIN1_ADDRESS: GAIN1_DEFAULT

CFG_ADDRESS: CFG_DEFAULT | CFG_GC_EN_ENABLED | CFG_GPO_DAT_HIGH | CFG_GPO_EN_ENABLED

Reading ADC signal AMC chips:

Every 100us the status is read. In case DRDY0 is active (new data available) the ADC register is read.

The description of SEC_FAIL is a little poor. Maybe you can give me more information about this error. Maybe this will give me a hint to find what is the problem source.

Thank you for helping me.

Franz