Other Parts Discussed in Thread: ADC12D1800, LMH6554, LM95241, ADC12DL3200EVM, ADC12DL3200, ADC12DL2500

Tool/software:

Hi,

1) I want to migrate my design which is currently using ADC12D1800 to new part ADC12DL1500. Is there any migration guide that's available?

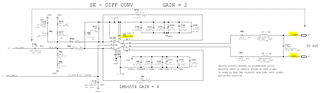

2) In the old part "V_CMO" pin was available which was used previously used as an input to VCM pin of LMH6554. In the new ADC which is the equivalent pin to that?

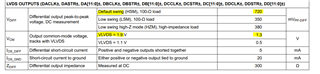

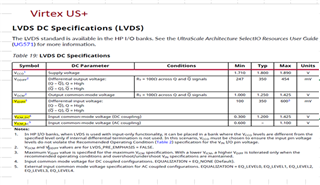

3) Previously we used all data lanes of DI, DID, DQ, DQD to interface with FPGA. With the ports renamed as LVDS A, B, C and D, how do these map to current ADC's DI/DID/DQ/DQD?

4) We plan to retain LM95241 for remote temperature sensing. Is that ok with ADC12DL1500?

Thanks