Other Parts Discussed in Thread: TSW14J57EVM,

Tool/software:

Hi,

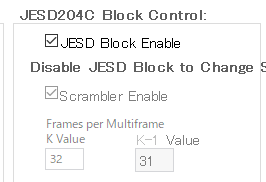

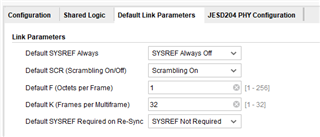

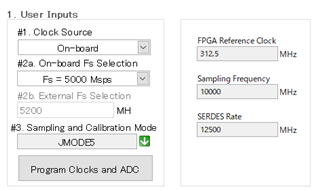

I am trying to check the operation of JMODE5 and am having problems.

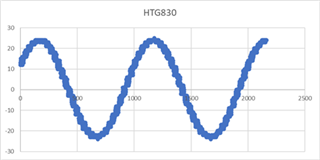

Configuration 1 was able to capture the sine wave input from the function generator to INA.

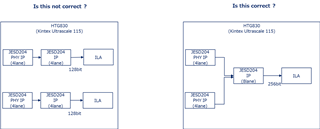

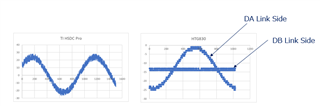

Configuration 2 was able to capture the sine wave for the DA link side data, but not for the DB link side.

When a sine wave was input to INB, the data on the DB link side was able to capture the sine wave, but the DA link side was not able to capture the sine wave.

Have there been any reports of similar problems in the past?

Are the two RX PHYs out of sync? I tried one PHY (8 lanes) as a test, but the data on the DB side is not sinusoidal, so I don't think it is a synchronization problem.

Color map of data acquired by ILA of Xilinx's JESD204 IP output signals.

When in ramp mode or transport layer test mode, both links appear to be storing data correctly.

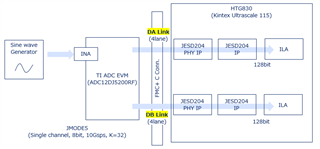

Test Configuration 1

TSW14J57EVM(RevE) + ADC12DJ5200RFEVM

Test Configuration 2

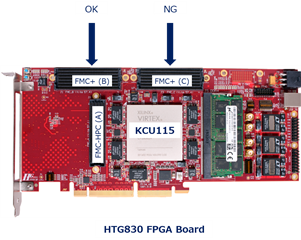

HTG830 (Hitech Global) + ADC12DJ5200RFEVM

Regards,

Takeo