Tool/software:

Hello,

I am using an ADS131A02 and an ESP32-PICO-KIT for my project. In this case, the ADS131A02 is in synchronous slave interface mode, as I will be using SCLK as iCLK. The problem is that I cannot get a response different from "0x7F8100" in the SPI communication.

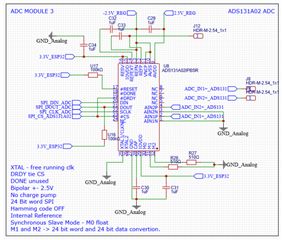

I have attached the circuit schematic:

It is also important to consider everything shown in the image, as it contains all the proposed configurations. One of the most important is that the word size is 24 bits, with hamming disabled, SCLK as iCLK, no charge pump. Finally, I do not have a pull-up resistor for the CS pin because I am using the internal pull-up of pin 15 (CS0).

I have also attached the code used:

I know the error could be in the programming or the schematic because when I measure the REFP value, it gives me 1.25 V by default but negative, relative to GND. The capacitors are non-polarized ceramic capacitors. I appreciate your help as I have tried to solve this and haven't been able to.