Tool/software:

This is a 1 Msps ADC. The datasheet say the 'edge jitter' must be 10 ps max.

1) I am not sure what 'edge' jitter means. Is this a cycle-to-cycle jitter? I'm assuming it means something like this below.

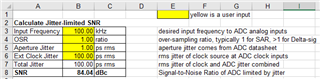

2) Why is this to tight? 10 ps is 10 ppm of 1 MHz. It seems like you can trigger CONVST at any rate you like up to a max of 1 Msps, so why would this jitter matter? I don't even see how it could be SNR related; I am not sure i did the calculation correctly, but I believe maintaining a >93 dB SNR at 100 kHz would still only imply something like 100 ps jitter.

I wanted to use something simple like a silicon oscillator for CONVST, but the jitter of these is much higher. What are the practical performance effects if I use a clock with e.g 100 ps jitter.

I have some additional questions about the digital outputs but since that is a different topic I'll put them in anew question.