Tool/software:

Hi,

I am using LMP92066 device for PA GaN and LDMOS biasing in the design.

Kindly guide me to configure the device for biasing purpose.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Vaishak,

To get started, first you must determine what you want your DAC output to be at 24C. This is your BASELINE code. You will then need to figure out the correct transfer function for your PA and calculate the coefficients to program into the LUT. The datasheet explains this in detail. When you have all of the data, you then need to program the device and burn the EEPROM. Let me know if you have any specific questions about this procedure.

Thanks,

Erin

Hi Erin,

For GaN configuration, i want to achieve the below sequence-

1.) FETDRV1 and FETDRV0 should be -5V at 24C

2.) Then after 5 seconds FETDRV1 should be set to -2.8V.

3.) Then after 10seconds FETDRV0 should be set to -3.7V

for LDMOS configuration, i want to achieve the below sequence-

1.) FETDRV1 and FETDRV0 should be +5V at 24C

2.) Then after 5 seconds FETDRV1 should be set to 2V.

3.) Then after 10seconds FETDRV0 should be set to 1.9V.

Hi Vaishak,

I don't believe the device has a timer to set different voltages. You will need to use a microcontroller to manually set the voltages.

1) FETDRV1 and FETDRV0 should be -5V

At startup, ensure that the DRVEN0 and DRVEN1 pins are set to GND. This will force the FET outputs to be equal to VSSB, which you can set as -5V.

2) Then after 5 seconds FETDRV1 should be set to -2.8V.

3.) Then after 10seconds FETDRV0 should be set to -3.7V

There are a couple of ways you can do this, depending on if you wish to use the temperature compensation functionality or not.

Without Temperature Compensation: Set the DAC1M_OVRD = 0x07 and DAC1L_OVRD =0x0A. Set DAC0M_OVRD = 0x04 and DAC0L_OVRD = 0x28. Set OVRD_CTL = 0x02. This will enable the DACs to output the specific voltages. Then after 5 seconds, set DRVEN1 to high to enable FETDRV1. After 10 seconds, set DRVEN0 to high to enable FETDRV0. The DAC outputs will be static and not affected by temperature changes.

With Temperature compensation: Set DAC0_BASEM, DAC0_BASEL, DAC1_BASEM, DAC1_BASEL to the values instead of the ORVD registers. You will need to populate the LUT coefficients for temperature compensation to work. Similar to the other sequence, you will need to control the DRVEN inputs manually to set the FET outputs.

For LDMOS, are you sure you want +5V on the output? That would set the PA fully on, which in many cases is not ideal during startup.

Thanks,

Erin

Hi erin,

Thank you so much for your inputs. We really need your support as we are developing RFE for the first time.

Also, the LMP92066 DRVEN pins are controlled by the MpSoC (it's a SoC +FPGA combined) microcontroller.

I have few more questions -

1.) should both the DRVEN pins be controlled seperately in order to achieve the previously told biasing sequence?

Can we short both the pins and controll both the DRVEN using single connection?

2.) For the last question you asked, as per the sequencing told by the PA manufacturer (NXP), For LDMOS initially I need to set the voltage to +5V, Then after 5 seconds FETDRV1 should be set to 2V. Later after 10seconds FETDRV0 should be set to 1.9V.

Your support is highly appreciated, please help us clear all these doubts as it is very crucial for us.

Regards,V

aishak B

Hi erin,

There was some wrong information received from the PA vednor. For the above query number 2, After the GaN power ON sequence is completed. The LDMOS bias Voltage of FETDRV0 has to be set to 2V, Then after 10 seconds FETDRV1 has to be set to 1.9V.

regards,

Vaishak B

Hi Vaishak,

1.) should both the DRVEN pins be controlled separately in order to achieve the previously told biasing sequence?

If you would like there to be 5 seconds of separation between the FETDRV outputs, you would want to control the DRVEN pins separately.

2.) So, our PA controllers are designed with the intention of setting the outputs to minimum voltage at power up. You will have to implement a slightly different sequence in this case:

-For the LDMOS controller, Set the DAC1M_OVRD = 0x0F and DAC1L_OVRD =0xFF. Set DAC0M_OVRD = 0x0F and DAC0L_OVRD = 0xFF. Set OVRD_CTL = 0x02. This will set the DAC outputs to 5V. With this, you will also want to set the DRVEN0/1 inputs to HIGH, to set the FETDRVs to 5V. This should likely be the first thing you will want to do. Then you should do your GaN powerup, then do the LDMOS powerup. For the LDMOS voltage changes, you would just set the DACxx_OVRD registers to new values to correlate to the required DAC output. 2V = 0x0666, 1.9V = 0x0614.

Thanks,

Erin

Hi Vaishak,

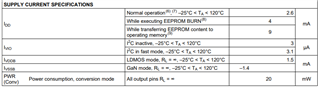

You can see some basic power consumption information in the datasheet:

In addition, each FET output can handle 10mA of additional current from the PA. This would be added to the VSSB or VDDB current.

Thanks,

Erin

Hi Vaishak,

The typical power dissipation is 20mW. This power dissipation will change depending on how much current the DAC outputs are sourcing to the PAs.

Thanks,

Erin