Tool/software:

Hi,TI's specialist.

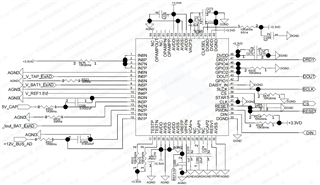

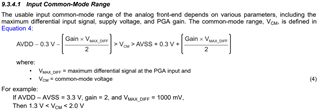

When I used ADS131E08 to collect data, the data I returned was wrong, and I used RDATA command . The hardware interface is that the power supply AVDD = 3.3V, the internal clock of the chip is 2.048MHZ, and the single-ended signal is input with (CH1~CH6).

The MCU used is C2000 DSP280039, and my software configuration process is as follows:

1. Initialize SPI, 4MHz, 16bit, Polarity 0, phase 0;

2. RESET ADS131e08 according to manual 11.1 Power-Up Timing;

3. Send SDATAC command and send STOP command;

4. Confg1 0xd2h, Multiple data readback mode, sampling rate of 16KSPS;

5、Confg3 0x40h, using external reference source (3V);

6、channel registers to configure 0x10h, with CH1~CH6 enabled and CH7 and CH8 disabled;

7、Send a START command;

8、 Change the SCLK frequency of SPI to 10Mhz;

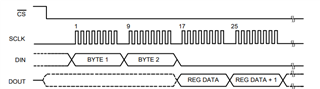

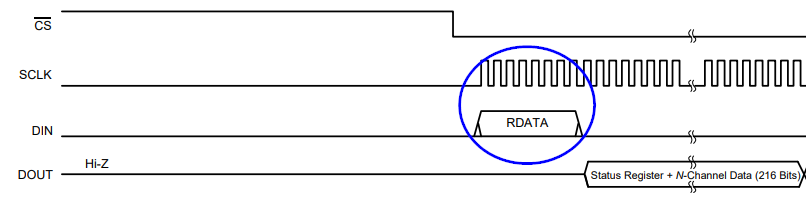

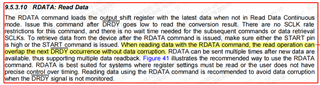

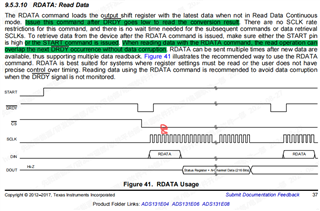

Next,I sent a RDATA command in the 15KHz EPWM interrupt function, and sent the remaining 216 SCLks to read the data of eight channels. The CS pin was kept low throughout the process. Because the interrupt frequency of 15K is asynchronous with the set sampling frequency of ADS131E08, there will be a phenomenon that the DRDY event overlaps with the reading data clock SCLK, but the manual says that it will not cause data corruption, which can be seen in the actual test.

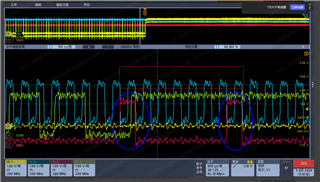

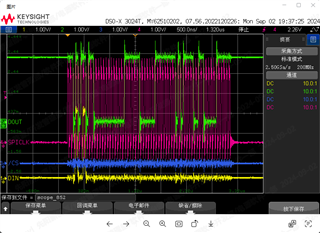

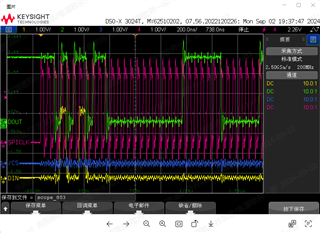

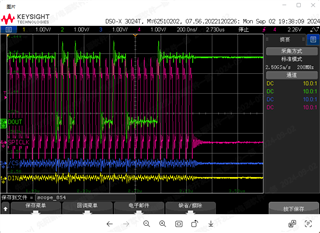

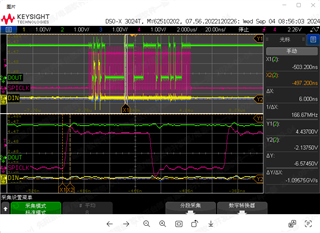

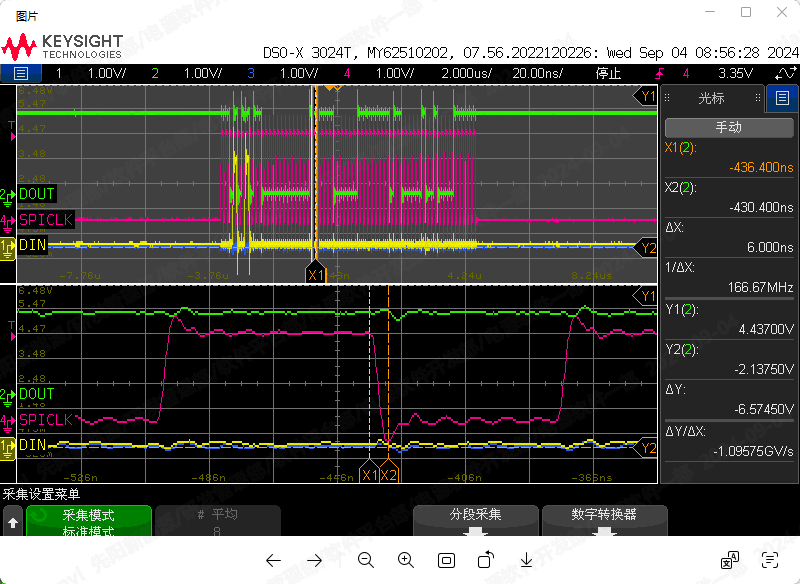

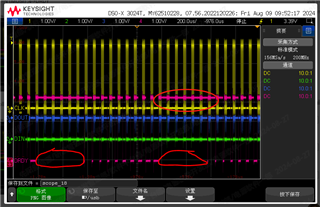

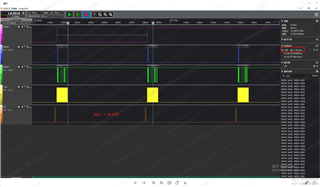

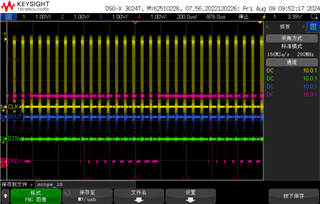

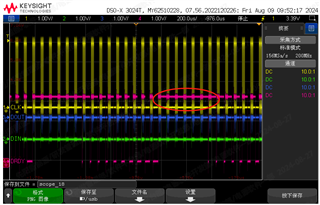

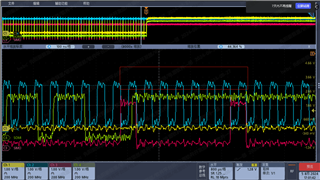

Oscilloscope waveform:

1-> SCLK; 2->DOUT (MISO); 3->DIN (MOSI) ;4->DRDY

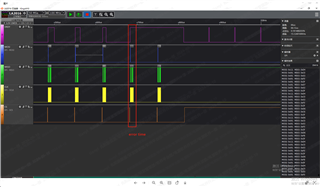

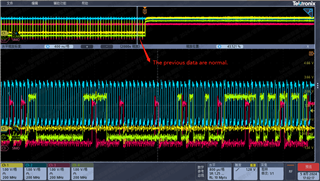

Data corruption occurs at the following moments:

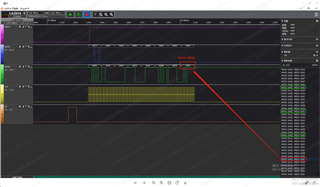

We did a test on related data errors time, and the test method is:

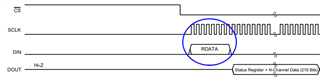

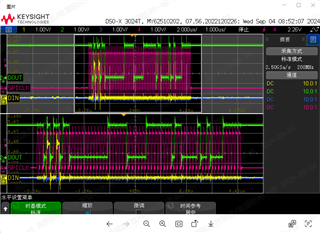

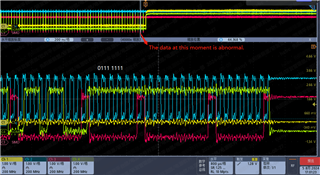

1、 Only the upper 8 bits of channel 2 data (the upper 8 bits of 24-bit data) are read, because the input of channel 2 is about 1.5V If the data changes suddenly, the upper 8-bit data will change. The difference between it and the above configuration is: SPI Polarity 1, phase 0.

2、If the high 8bit data will change, pull up the CS pin and grab the oscilloscope waveform through it.

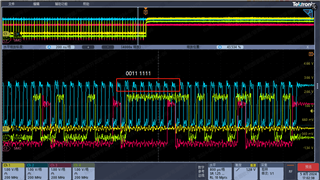

Waveform at normal time of data: 1: CS; 2、SCLK; 3、DIN (SIMO) ; 4、DOUT(SOMI)

Normal data high 8 bits 0011111 :

High 8 bits of data at abnormal time 011111 :

Finally , Does the DRDY event really affect data reading when using the single conversion instruction RDATA?

We want to know what the problem is. Looking forward to your reply, thank you!