Other Parts Discussed in Thread: TMUX7209, OPA827, OPA828

Tool/software:

Hi Team

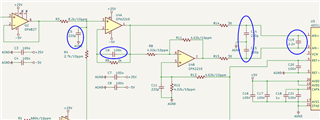

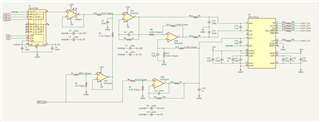

I am encountering a problem while multiplexing ADS127L21 using analog switches, as shown in the schematic below.

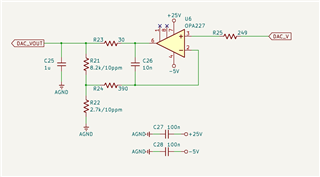

VIN_1, VIN_2, and VIN_3 are all DC signals, R3 and R4 form a voltage divider in order to extend the input range up to 20V. U3A provides an offset of about 30mV to prevent ADC saturation. The two OPAs of U4 are used to convert input signal from single-end into differential, and the common voltage is obtained by R10 and R13 from REF voltage division.

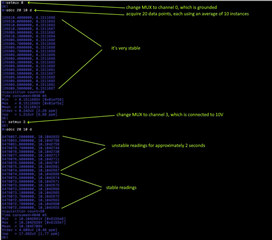

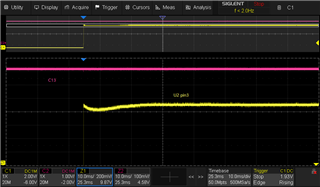

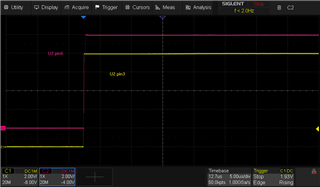

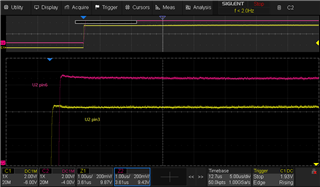

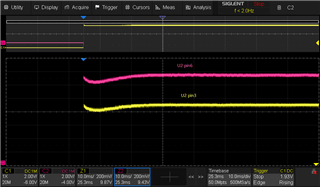

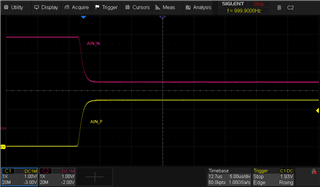

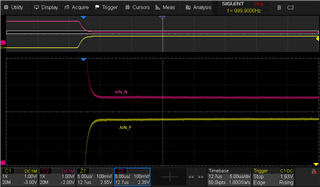

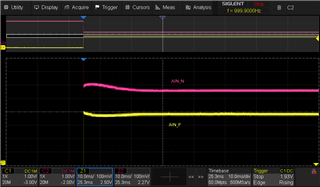

The problem is that when the MUX switches between two voltages with large differences, it takes a long time for the measurement value to stabilize at a few LSBs.

For example, set VIN_1 = 10V, then switch the MUX from S1 to S2 and delay a dozen milliseconds which I think is enough. Then the ADC makes continuous measurements. It can be observed that the first measurement value has an error of approximately dozens of uVs, and then the error gradually decreases, and stabilizes to a constant value after about 1 second.

The stabilization time depends on the voltage difference when switching, the greater the voltage difference, the longer the time takes. According to my tests, the relationship between them is not linear, so it cannot be calibrated out.

This problem has been bothering me for many days, and I can't find any theoretical support for this phenomenon by analyzing the circuit. Can you give me some inspiration from experience?

Best regards.