Tool/software:

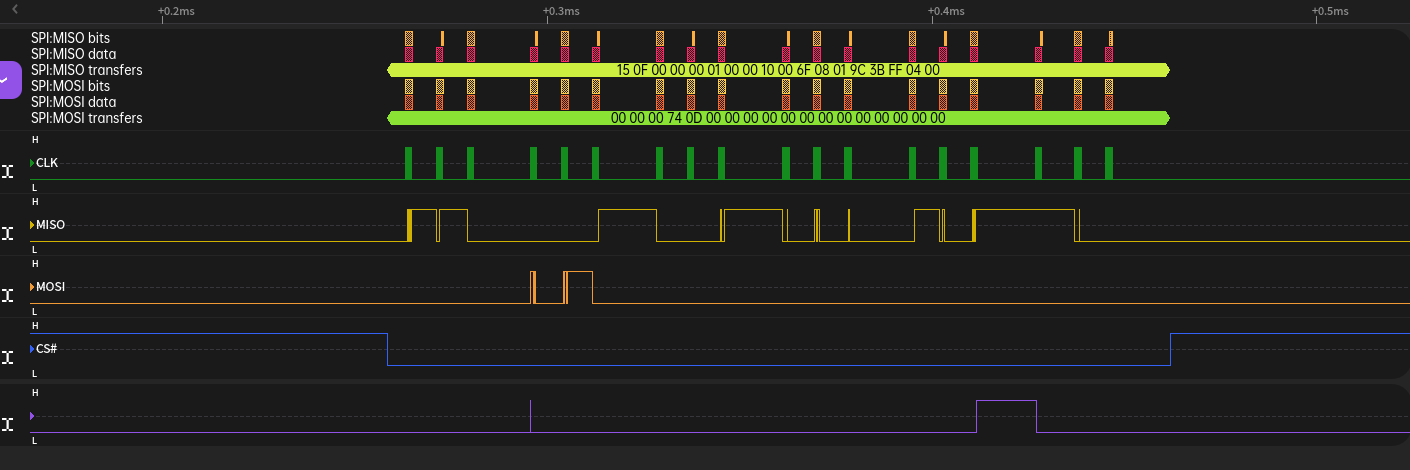

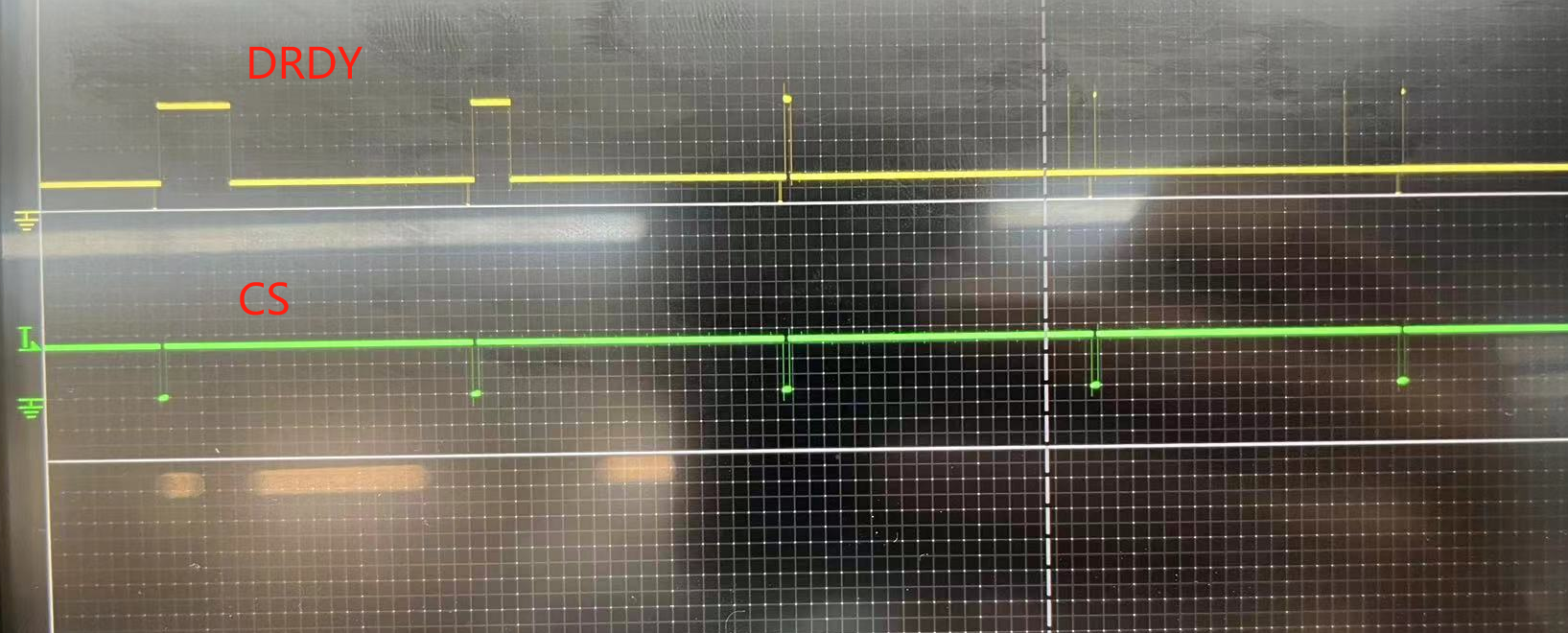

When the MCU communicates with the ADS131B04 SPI, it is observed through the oscilloscope that the DRDY signal is mostly kept low in the SPI timing, and there will be a jump when there is data transmission, is this correct? Because I see that the DRDY written on the data sheet seems to be always high, providing a falling edge when there is data ready

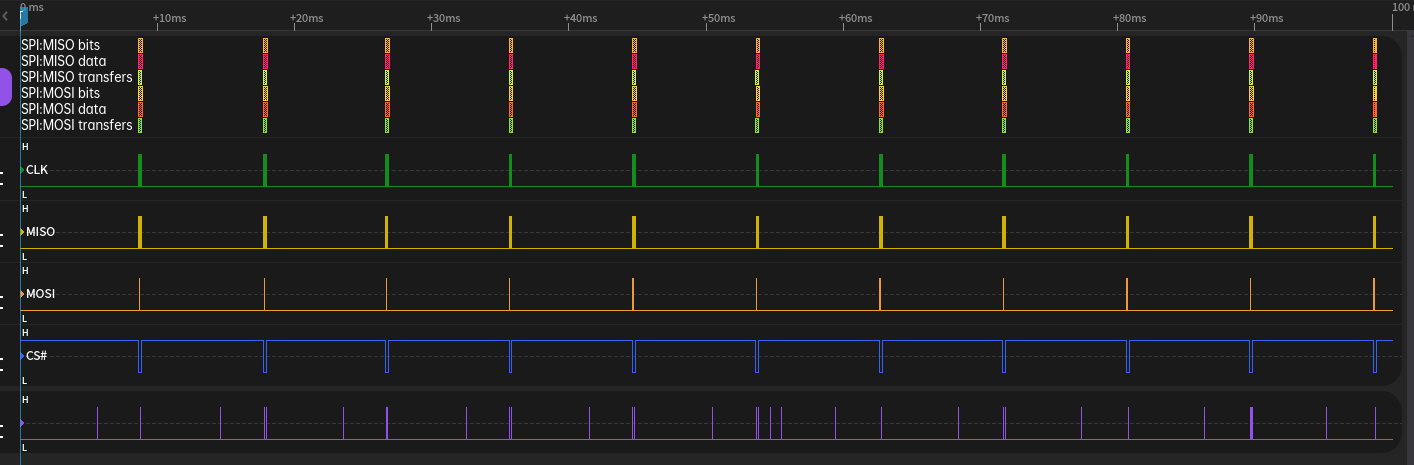

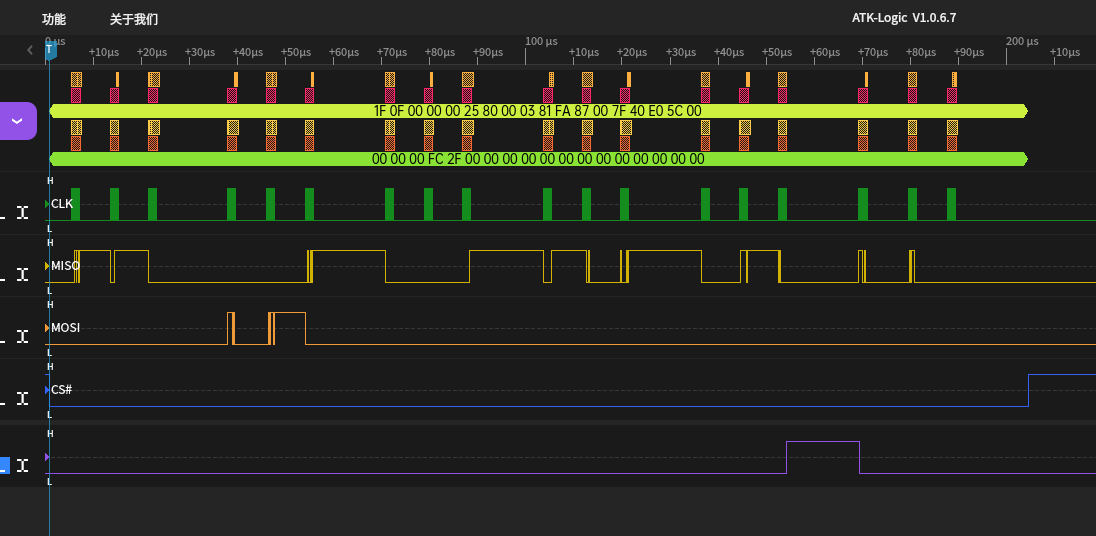

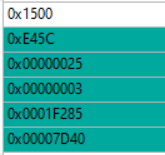

Can you see this?GC_DLY[3:0] is set 1110b(32768/(4.096*10^6)), but the sample period is set 10ms

Can you see this?GC_DLY[3:0] is set 1110b(32768/(4.096*10^6)), but the sample period is set 10ms