Tool/software:

Hi all,

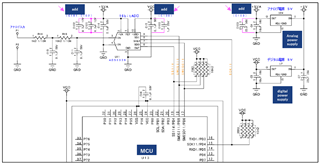

Analog signals are input to MCU using ADS8339.

The lower 3 bits of ADS8339 are become biased towards 1 or 0.

For the Vref and Vbd parts

It is improved by adding capacitor capacitance.

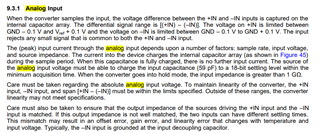

1)Is the approach that it is improved by changing capacitance value and voltage value of Vref correct?

2)It says "The analog power supply must always be greater than or equal to the digital power supply." in the datasheet.

Is the following combination acceptable?

Analog power +VA=5 V±1% (4.95~5.05 V), Digital power +VBD=5 V±1% (4.95~5.05 V)

Best Regards,

Ryusuke