Tool/software:

Hello experts,

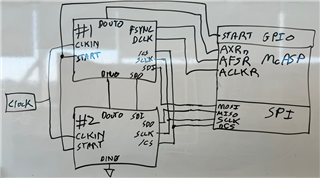

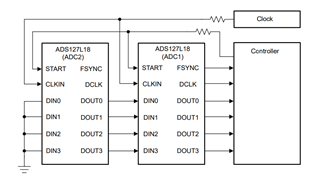

Would it be possible to check my thinking on the implementation of the ADS127L18 ADC through a block diagram?

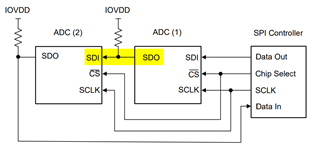

Essentially, we're daisy chaining 2 ADCs together and interfacing with one of them (let's call it #1) through McBSP. However, this is the part I'm concerned about: we want to use McBSP in SPI mode for the initial configuration of registers, while switching back to normal McBSP operation for reading data. Since MDR is the only pin that overlaps between the two protocols, we are using a demux to switch between the two modes. I am only worried about the digital side, so the analog part is not shown. Could you let me know if you think this setup will work, and, if not, why? Sorry if the photo is unclear, I'll gladly answer any questions you have.

Thank you,

Dylan