Tool/software:

Hello,

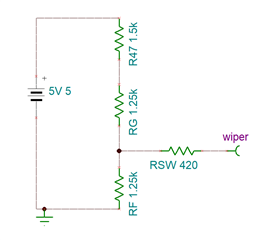

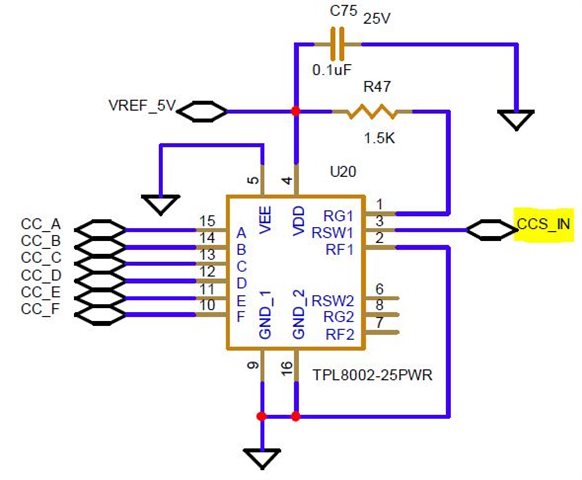

I have read your switch truth table from the data sheet and just need some additional clarification. I was given a circuit using your device that I need to evaluate, but want to make sure what resistance to expect at the RSW1/2 outputs as the circuit I am evaluating uses the RSW1 output and connects to a non-inverting input of an external differential amplifier while the inverting input connects to gnd (opposite of the data sheet description). The external amplifier will ultimately produce a 100uA constant current source. I understand the wiper has a constant resistance of 420 ohms, with a setting of 32 (b100000) will the RG and RF terminals cancel (0 dB attenuation) and only the 420 ohms of resistance is observed at RSW1? Circuit configuration shown below, maybe a couple of additional setting examples would help.

Thanks,

Kevin