Tool/software:

Hi,

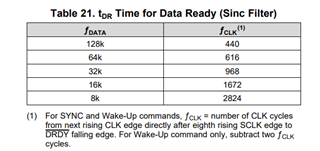

in ADS1282-SP Datasheet Rev.B page 9, section 7.7, the parameter tDR is defined.

Below you see a reference to Table 21 for SINC filter while an equation is provided for FIR filter respectively (which I think shall be combined to get the same tDR for both filter)

My question is how tDR is calculated for each filter?

BR, Hang