Tool/software:

Hi team,

Regarding programmable hysteresis comparator in DAC53204-Q1, MCU needs to write commands in RST-CMP-FLAG-X bit at each latch cycle. Is my understanding correct?

Best regards,

Shunsuke Yamamoto

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

Regarding programmable hysteresis comparator in DAC53204-Q1, MCU needs to write commands in RST-CMP-FLAG-X bit at each latch cycle. Is my understanding correct?

Best regards,

Shunsuke Yamamoto

Hi Yamamoto-san,

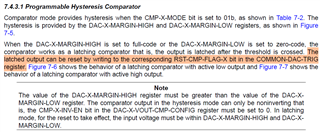

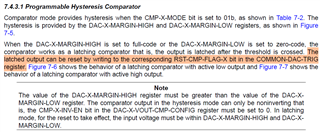

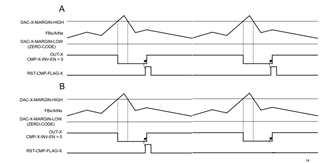

You only need to use the reset command if the comparator is configured in latching comparator mode. In normal (non-latching) mode, the comparator output will respond like the below figure 7-5:

Figures 7-6 and 7-7 are window comparators with a latching output.

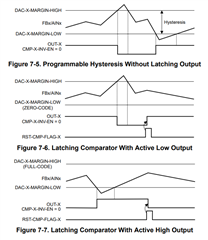

The latching output mode is set in COMMON-CONFIG. This setting will be in effect for any channel configured in window comparator mode:

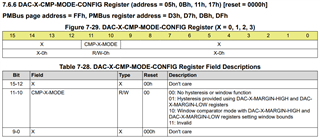

You can select if the device is in window comparator mode, or hysteresis mode in the DAC-X-CMP-MODE-CONFIG register:

If the margin high, or margin low code is set to full-scale, or zero-scale, respectively in hysteresis mode, then you do need to use the reset command. This is because the comparator input cannot pass full or zero-scale code to achieve the hysteresis, and the output will be stuck.

Best,

Katlynne Jones

Hi Katlynne-san,

Thank you for the reply. I mean my customer's use case frequently crosses the high threshold of comparator which is DAC-X-MARGIN-HIGH, so My customer would like to confirm if he needs to send logc high to RST-CMP-FLAG-X bit to frequently. I have created the image explaining what my customer plans to do. Could you please kindly answer which one is correct behavior A or B?

Best regards,

Shunsuke Yamamoto

Hi Yamamoto-san,

The images you share show the margin high, or margin low code is set to full-scale, or zero-scale, respectively. Is this how the customer plans to use the device? If so, then yes, they will need to use the reset command as shown in the figures.

Best,

Katlynne Jones

Hi Katlynne-san,

Thank you for the reply.

Is this how the customer plans to use the device?

Yes.

If so, then yes, they will need to use the reset command as shown in the figures.

Which one A? or B?

A has reset command on RST-CMP-FLAG-X bit at each cycle. Conversely, B has only one reset command on RST-CMP-FLAG-X bit at total cycle.

Best regards,

Shunsuke Yamamoto

Hi Yamamoto-san,

Figure A. The device can not satisfy the hysteresis if the low hysteresis is set to zero code. So, every time the high threshold is passed, a reset command will need to be set to reset the comparator flag when desired. The flag will not reset itself as shown in figure B

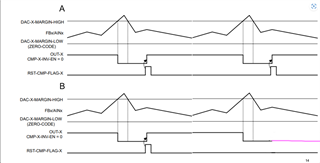

This is basically a latching comparator function with a latch on the low to high transition past the high threshold. Figure B would actually have the following behavior:

Best,

Katlyne Jones

Hi Katlyne-san,

Thank you so much for your answer. This is just a technical feedback from the customer. My customer prefers B operation because A operation takes many MCU resources compared with B operation. Internal core of MCU is needed to frequently send signals to DAC53204-Q1, so it makes the system higher performance MCU. May I know if you have any ideas to solve my problem? Sorry for bothering you.

I have listed the project information on this note. Thank you for the support.

Best regards,

Shunsuke Yamamoto

Hi Yamamoto-san,

It is no problem! The customer should only use this mode if they want a latching comparator. Meaning the output will stay latched until a reset command. If they want the comparator output to reset on its own like shown in figure B, then I'm thinking they don't want a latching comparator. Let's figure out what they do want.

In figure B, under what condition do they want the comparator output to reset? There must be something to indicate that the output can return to the normal state.

I understand that if the comparator input passes some high threshold, the comparator output should go high, when do they want the comparator output to return low?

Best,

Katlynne Jones