Tool/software:

Hello E2E,

This inquiry applies to a critical long duration space flight mission.

The SCL/SCLK pin when used as SCL in an I2C interface is specified with a maximum spike suppression (Tsp) of 10ns to 50ns depending on interface speed.

When the SCL/SCLK pin is as used as SCLK in a SPI interface is there any spike suppression applied to the SCLK within the AFE11612, if yes what is the max spike interval that is suppressed ?

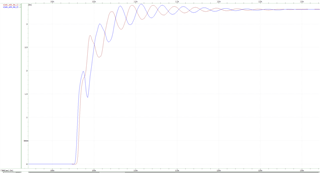

More specifically can the SCLK pin when used in a SPI interface tolerate non-monotonic rising and falling edges, our SI simulations are showing some non-monotonic edges on SCLK, need to know if that could cause "false-clocking" ?

Thank you,

-John