Tool/software:

Dear sirs,

I am working with ADC34J45 and I have a problem related to the phase noise with the digitized signal.

Configuration of ADC34J45 is shown as follows:

- Input frequency = 47.4 MHz -20dBm Without modulation

(-84dBc to 25KHz offset with BW=25KHz)

- Frequency clock: 158.4MHz LVDS Level about 0 dBm to the input of ADC

(85dBc adjacent channel to 25KHz offset (BW=25KHZ))

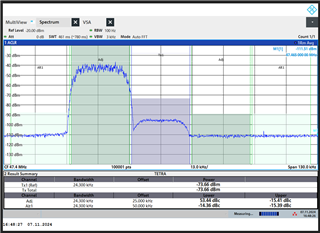

But the signal digitized by ADC is showing a high phase noise and very bad adjacent channels

Please, find below the digital signal analysed with MATLAB.

Zoom in 47.4MHz:

As you can check, phase noise is very bad in comparison with the phase noise of input signal and the clock signal.

I have checked the power supply increasing the DC filter to the input of low noise LDO which is used to supply +1.8AVDD to the ADC. I am using LDO from Texas TPS7A9101DSK.for 18AVDD.

Please, find attached a file with the samples of ADC, the values in the file are multiplied by 4 related to the output of ADC.

Finally, the inoput impedance of ADC is 200 ohms, and therefore the 0dBFS is about +4dBm.

Please, could you help me witth this issue?

Thanks in advance.

Best Regards,

Pedro