Tool/software:

Hi team,

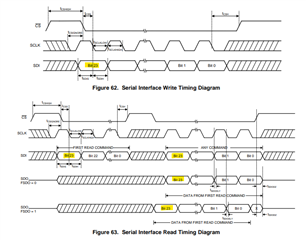

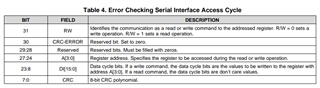

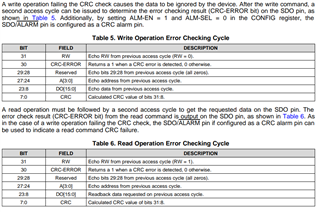

Customer is asking how the SPI write & read timing diagram with CRC polynomial work. So could you give examples of SPI write & read timing diagram with CRC polynomial? In case of write operation, could you also add the second access cycle to to determine the error checking result?

And according the datasheet as below, by setting ALM-EN = 1 and ALM-SEL = 0 in the CONFIG register, the SDO/ALARM pin is configured as a CRC alarm pin. Could you also give examples of how the CRC alrm pin work?

Regards,

Noriyuki Takahashi