Tool/software:

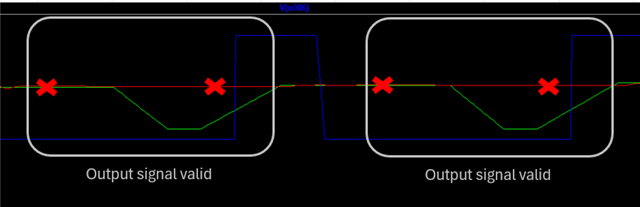

We're using a sample hold circuit ahead of the 9218 and then performing 2 conversions and averaging the result. Is there a timing diagram that notes when the A/D is sampling it's input so I can assure that my input signal is in a valid state? In the diagram below the green trace is the raw signal, the red line is the output of my S/H and ideally, I'd like to align the ADS9218 to sample at the red x marks.