Tool/software:

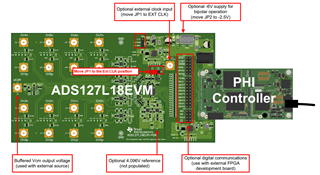

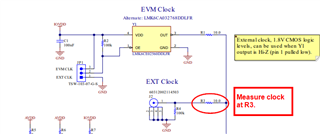

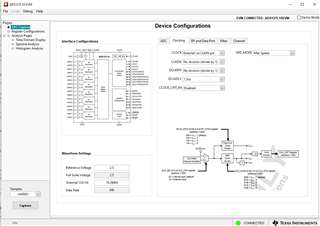

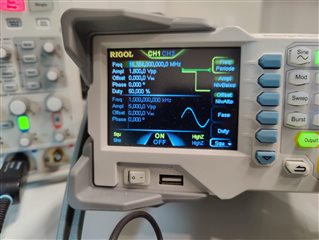

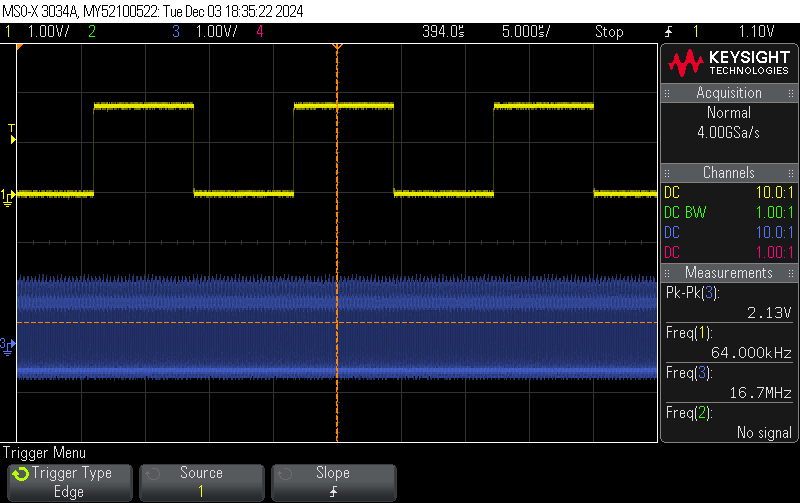

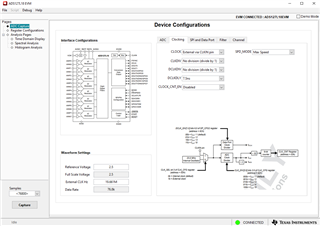

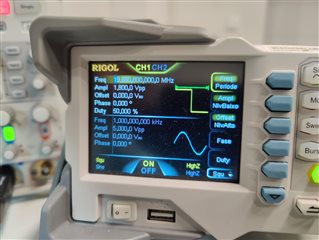

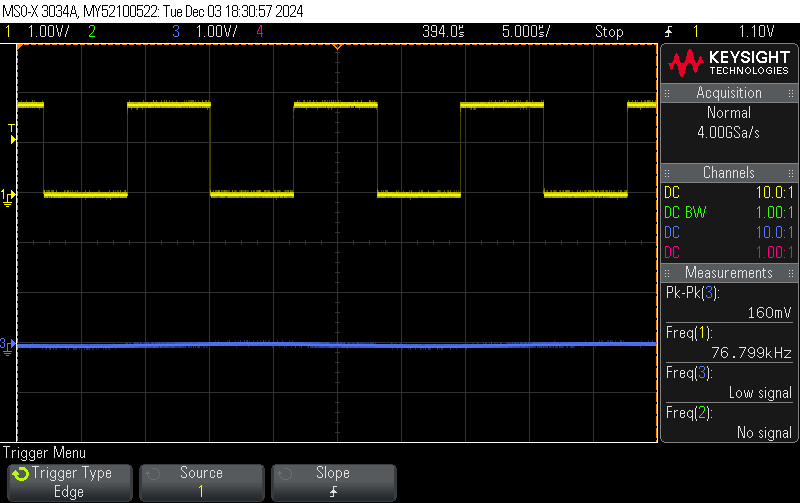

I am experimenting with the ADS127L18EVM Board, by using both the PHI controller board and standalone hardware programming and I am having trouble with the data rates. Using an external generator to generate two frequencies 16.384MHz and 19.6608MHz I need for my application, for an output data rate of 64KHz and 76.8KHz, respectively, the device performs differently. When I set the frequency to 19.6608MHz and the filter to wideband, OSR=128, by probing the FSYNC pin in J3 Header, I get a FSYNC with the expected 76.8KHz, however, when setting the generator to a frequency of 16.384MHz, I get a FSYNC with a frequency from 95KHz to 125KHz, without changing any settings. I also tested this with the sinc filters at OSR= 128 and got the same strange result. However, by accident I discovered that when connecting another probe from the oscilloscope to the CLKIN pin of the ADC, to check the input CLK frequency, I now get the correct 64KHz. I tested this with different Oscilloscopes and got the same result. I also tested it with the 32.768MHz crystal present on the EVM, with Filter set to Wideband, OSR=128 and CLKDIV=2, to get a data rate of 64KHz and it worked as expected, I got the 64KHz FSYNC signal and it made no difference probing the CLKIN pin.

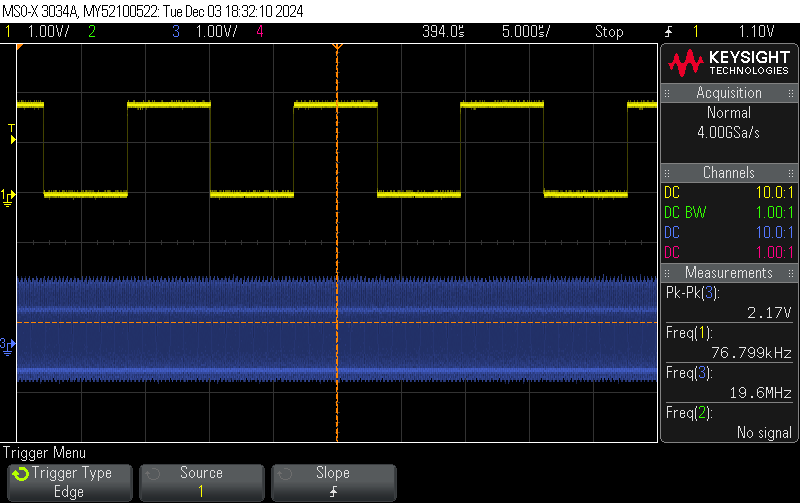

I will attach some pictures from the EVM software, the signal gen and the oscilloscope:

As you can see, different behavior while probing and not probing the CLKIN pin for 64KHz.

As you can see, no change in behavior while probing and not probing the CLKIN pin for 76.8KHz.

Can you help us identify the problem?