Other Parts Discussed in Thread: TX7332

Tool/software:

I am not sure if I understand the AFE_PDN_FAST specifications

1) AFE_PDN_FAST requires 8us to wake up

2) but only if last woken up <500us previously, failing which it requires 4ms to power up.

What method is recommended to keep the device in partial power down (and not fully powered down)?

If a (-ve) pulse is sent every 500us for 18us? or is a longer pulse required (and for how long)?

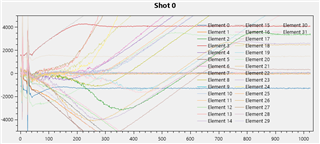

Our current operational sequence is as follows, but the automatic DC Offset indicates that the capacitors are still charging up after 18us (8+8+2us).

1) -ve pulse the AFE_PDN_FAST (wake up)

2) wait 8us for wake up

3) TX_Trig (to synchronise AFE)

4) power up the TX (using TX7332)

5) wait another 8us (for TX7332 to wake up)

6) pulse the TX7332

7) wait 2us for TX7332 to pulse and TR switch to activate

8) shut off power to TX7332.

8) start capturing on the AFE

9) end capturing

10) send AFE_PDN_FAST (+ve) to put AFE back into power down.

process the data and send to imaging.... and repeat.

Our processing takes <200us, so meeting the 500us requirement, yet the automatic DC-offset is not yet settled (in the 16us between AFE_PDN_FAST=0 to start capturing).

Please advise.