Tool/software:

Hello forum

I am using an Arria 10 FPGA as the receiver for this ADC.

The link is not working, and as far as I can tell the synchronization sequence is not completing (based on the fact that the SYNC_N signal remains low).

As a first step I would appreciate if TI could verify that the initialization sequence below is correct.

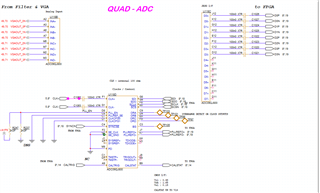

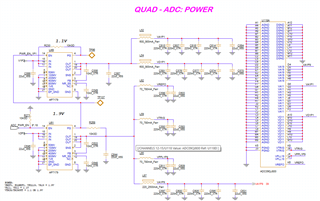

In addition, I have attached an excerpt of the relevant schematic.

The input clock to the ADC is LVDS 100MHZ. Note that the polling does succeed in steps 3, 16 and 17 below.

My desired sample F is 500MSPS.

Sequence I am using is:

1. Set Power On

2. Soft Reset (0x80 to 0x0)

3. Poll bit 0 in 0x270

4. CPLL Reset (1 to 0x5C)

5. VCO Bias (0x4A to 0x3F)

6. PLL (0x9 to 0x3D)

7. PLL (0x5 to 0x3E)

8. CPLL no reset (0 to 0x5C)

9. JESD EN (0 to 0x200)

10. CAL DIS (0 to 0x61)

11. JMODE (2 to 0x201)

12. KM1 (0x1F to 0x202)

13. Various (2 to 0x204)

14. Calibrate settings (1 to 0x62)

15. Calibrate settings (1 to 0x65)

16. POLL VCO CAL DONE, Poll bit 0 in 0x5E

17. POLL CPLL LOCKED, Poll bit 0 in 0x208

18. Enable CAL state machine (1 to 0x61)

19. Restart JESD (1 to 0x200)

20. Finished

Much thanks

David