Tool/software:

Hi,

I am working with the following setup:

CPU: iMX93

IC: ADS7950

SPI: LPSPI7 chip select on GPIO2 4

OS: Yocto Linux based on kernel version L6.1.22

I'm getting I/O error while trying to read ADC channel values in sysfs.

Below is the relevant device tree configuration:

lpspi7: spi@42710000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "fsl,imx93-spi", "fsl,imx7ulp-spi";

reg = <0x42710000 0x10000>;

interrupts = <GIC_SPI 193 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX93_CLK_LPSPI7_GATE>,

<&clk IMX93_CLK_BUS_WAKEUP>;

clock-names = "per", "ipg";

};

&lpspi7 {

fsl,spi-num-chipselects = <1>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_lpspi7>, <&pinctrl_lpspi7_cs>;

pinctrl-1 = <&pinctrl_lpspi7>, <&pinctrl_lpspi7_cs>;

cs-gpios = <&gpio2 4 GPIO_ACTIVE_LOW>;

dmas = <&edma2 83 0 0>, <&edma2 84 0 1>;

dma-names = "tx","rx";

assigned-clock-rates = <30000000>;

status = "okay";

adc@0 {

compatible = "ti,ads7950";

reg = <0>; /* SPI chip select 0 */

vref-supply = <®_5v>;

spi-max-frequency = <10000000>;

#io-channel-cells = <1>;

status = "okay";

};

};

pinctrl_lpspi7: lpspi7grp { /* LPSPI7: LPSPI7 IOMUX Pin Configuration */

fsl,pins = <

MX93_PAD_GPIO_IO07__LPSPI7_SCK 0x3fe

MX93_PAD_GPIO_IO06__LPSPI7_SOUT 0x3fe

MX93_PAD_GPIO_IO05__LPSPI7_SIN 0x3fe

>;

};

pinctrl_lpspi7_cs: lpspi7_cs_grp {

fsl,pins = <

MX93_PAD_GPIO_IO04__GPIO2_IO04 0x31e

>;

};

To debug the issue, I added logging in the TI ADS7950 driver code as follows:

Driver code:

diff --git a/drivers/iio/adc/ti-ads7950.c b/drivers/iio/adc/ti-ads7950.c

index 2cc9a9bd9db6..d4ce4917d1fb 100644

--- a/drivers/iio/adc/ti-ads7950.c

+++ b/drivers/iio/adc/ti-ads7950.c

@@ -377,6 +377,8 @@ static int ti_ads7950_read_raw(struct iio_dev *indio_dev,

if (ret < 0)

return ret;

+ printk("Address: %u\n", (unsigned int)chan->address);

+ printk("Extracted Value: %u\n", (unsigned int)TI_ADS7950_EXTRACT(ret, 12, 4));

if (chan->address != TI_ADS7950_EXTRACT(ret, 12, 4))

return -EIO;

Error:

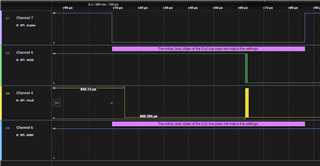

root@imx93-iwg50m-sodimm:~# cat /sys/bus/iio/devices/iio\:device1/in_voltage0_raw

[ 100.929228] Address: 0

[ 100.931641] Extracted Value: 15

cat: '/sys/bus/iio/devices/iio:device1/in_voltage0_raw': Input/output error

root@imx93-iwg50m-sodimm:~# cat /sys/bus/iio/devices/iio\:device1/in_voltage1_raw

[ 103.849178] Address: 1

[ 103.851563] Extracted Value: 15

cat: '/sys/bus/iio/devices/iio:device1/in_voltage1_raw': Input/output error

root@imx93-iwg50m-sodimm:~# cat /sys/bus/iio/devices/iio\:device1/in_voltage2_raw

[ 106.253289] Address: 2

[ 106.255694] Extracted Value: 15

cat: '/sys/bus/iio/devices/iio:device1/in_voltage2_raw': Input/output error

root@imx93-iwg50m-sodimm:~# cat /sys/bus/iio/devices/iio\:device1/in_voltage3_raw

[ 108.949172] Address: 3

[ 108.951597] Extracted Value: 15

cat: '/sys/bus/iio/devices/iio:device1/in_voltage3_raw': Input/output error

root@imx93-iwg50m-sodimm:~#

Could you please advise what might be causing this behavior or if there are any potential issues in my configuration or setup?

Regards,

Daniel