Other Parts Discussed in Thread: ADC08D1520

Tool/software:

Hello,

We are using ADC12QJ1600-SEP, and it is interfacing with Microchip PolarFire MPF500T-FCG1152. In the past we used TI ADC08D1520, but now with the new hardware we upgraded our board to TI ADC12QJ1600-SEP. We are very new to this chip and JESD technology. I need support with the configuration of the ADC12QJ1600-SEP. The following is the sequence and status of the ADC configuration registers. Can you please confirm and let me know if the ADC is configured, before we start debugging on the FPGA side. If it is not configured, then please suggest the changes required for the configuration sequence. Basically, we are following the ADC configuration sequence and steps from the following document:

Hardware has all 8 lanes connected to the FPGA.

I would like to use JMODE9 (8-bit, 8B/10B encoding, 8 lanes),

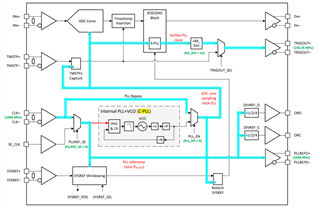

Clocking setup for ADC

Current, configuration Sequence for ADC is:

Pins: PLL_EN = '0'; PLLREF_SE = '0'; are tied to GND. CLK+/- = 1000 MHz;

Step1. PD = '1' (Right now ~40 us)

Step2. PD = '0' (Right now ~40 us)

Step3: Issue SOFT_RESET: Write register - CONFIG_A (Address: 0x000; Value: 0xB0)

Step4: Wait for 1280 ns (as per specification, it needs to wait 750 ns)

Step5: Read INIT_STATUS: Read register - INIT_STATUS (Address: 0x030)

Step6: INIT_STATUS Register value is "0x01" (Value we are reading right now)

Step7: Read VENDOR_ID: Read register - VENDOR_ID (Address: 0x00C)

Step8: VENDOR_ID Register value is "0x0451" (Value we are reading right now)

Step9: Stop JESD204: Write register - JESD_EN (Address: 0x200; Value: 0x00)

Step10: Stop Calibration: Write registers - CAL_EN (Address: 0x061; Value: 0x00)

Step11: Default to High Performance mode

Step12: JMODE selection: Write register - JMODE (Address: 0x201; Value: 0x09)

Step13: Desired KM1 value: Write register - KM1 (Address: 0x202; Value: 0x1F)

Step14: SYNC_SEL: Write register - JCTRL (Address: 0x204; Value: 0x0B)

Step15: JSYNC_N: Write register - JSYNC_N (Address: 0x203; Value: 0x01)

Step16: ALM_MASK: Write register - ALM_MARK (Address: 0x2C2; Value: 0x02)

Step17: Calibration settings: Write register - CAL_CFG0 (Address: 0x062; Value: 0x01)

Step18: Calibration settings: Write register - CAL_CFG1 (Address: 0x065; Value: 0x01)

Step19: Enable TRIGOUT: Write register - TRIGOUT_CTRL (Address: 0x057; Value: 0x81)

C_PLL is disabled, so not reading VCO_CAL_STATUS register at this time

Step 20: Enable Calibration: Write register - CAL_EN (Address: 0x061; Value: 0x01)

Step 21: Enable Over-range: Write register - OVR_CFG (Address: 0x213; Value: 0x0F)

Step 22: Re-start JESD204: Write register - JESD_EN (Address: 0x200; Value: 0x01)

Step 23: Clear ALM_STATUS: Write registers - ALM_STATUS (Address: 0x2C1; Value: 0x3F)

Step 24: Enable Calibration: Write register - CAL_PIN_CFG (Address: 0x06B; Value: 0x00)

Step 25: CAL_SOFT_TRIG: Write register - CAL_SOFT_TRIG (Address: 0x06C; Value: 0x00)

Step 26: CAL_SOFT_TRIG: Write register - CAL_SOFT_TRIG (Address: 0x06C; Value: 0x01)

Read all Status Register

VCO_CAL_STATUS: (Address: 0x05E) - Value we read is (0x02)

JESD_STATUS: (Address: 0x208) - Value we read is (0x64)

ALM_STATUS: (Address: 0x2C1) - Value we read is (0x00)

CAL_STATUS: (Address: 0x06A) -Value we read is (0x0F)

>>>>>btw, where are the Calibration Status Codes

We looked at TRIGOUT+/- and it is as expected ~156.5 MHz.

Based on the current status, please let me know the status of the ADC and what else do we need to do because the JESD interface in the FPGA (Microchip) is coming up with CGS_ERR. If you think ADC is in good state and nothing needs to be done, then we will look into the FPGA side

Thanks

Madhu