Other Parts Discussed in Thread: DAC38RF82

Tool/software:

Hello,

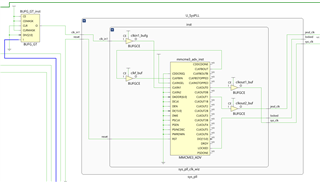

I have created the following setup to drive the clocks of DAC38RF82 from a Kintex Ultrascale FPGA.

External Clock 50MHz is fed to FPGA to create a 200MHz clock reference for the DACClk.

From the 200MHz, I use the internal DAC PLL to create a 6600MHz sampling clock and output a divided reference version from the DAC to a 550MHz reference clock (I also use an external divider to achieve 6600/12=550).

I then feed the 550MHz to the MGT Clock reference of the TI-JESD204 core.

From there, I use the mgt_tx_userclk2 (68.75MHz) to feed an MMCM PLL and generate 275MHz for my logic and a copy of 68.75 MHz as tx_sys_clock for the JESD204 core. See the diagram below.

The documentation of the JESD204 core says that mgt_tx_userclk2 does not need a BUFG because it is included inside the core.

As VIVADO implementation complaint I explicitly used a BUFG_GT to drive the PLL.

VIVADO implementation continues to fail with the following message:

[DRC REQP-123] connects_CLKINSEL_VCC_connects_CLKIN1_ACTIVE: U_SysPLL/inst/mmcme3_adv_inst: The MMCME3_ADV with CLKINSEL tied high requires the CLKIN1 pin to be active.

Questions:

1. Is the clocking scheme presented acceptable?

2. Is there a problem driving a PLL from mgt_tx_usrclk2 internally?

3. If it is a problem can I route the signal to a pin and provide to the PLL input clock the same signal from external pins?

4. Is there any reason that mgt_tx_usrclk2 has jitter that is not acceptable from MMCM?

Thanks,

Ilias