Other Parts Discussed in Thread: OPA192,

Tool/software:

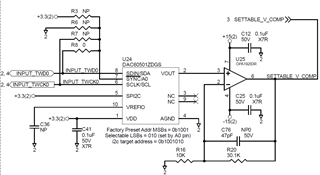

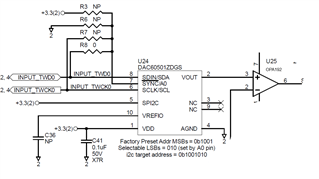

We have a new PCB we've spun that incorporates that DAC60501ZDGS, which according to the data sheet, should power up at zero V out.

As you can see, we're trying to run the DAC off 3.3V. In addition, you'll see we're trying to run it in i2c mode. For the i2c address, we desire 0x02 (010), so we've tied A0 to the i2c data line.

Before I've even tried to write/read to the command registers, upon powerup, I'm observing Vout is around +830mV. More concerning, I'm observing VREFIO reading about 3.23V. If I understand the data sheet and the power on state of the chip, VREFIO should be an output and I should be seeing the internal 2.5V signal present.

Thinking we were doing something odd, we whitewired the 3.3(2) rail to be 5(2) on a second board. Upon doing this, the VREFIO measured 2.5V dead on, which was nice to see. However, Vout was measuring not zero, at +908mV.

The 3.3V measurements were made on one PCB, and the 5V config was done on a second. So I have 2 boards with DAC60501s that are exhibiting this problem. In addition, I lifted the pin on the OPA192 on the 5V config, to ensure the DAC60501 was unloaded, and it still exhibited this behavior.

The part markings on the chip are as follows:

TI27

P30RA

651Z

I attempted to communicate via i2c, and this appears to be working. I can write registers and read them back. I know I'm truly talking to the chip, due to the ACKs I'm seeing on the i2c bus, plus when I read the DEVID register, the non reserved RESOLUTION and RSTSEL bits are set appropriately. I can also write to the DAC CODE register and read the value back. However, Vout stays at the above mentioned voltages. Post power up, I've tried issuing a SOFT RESET via the TRIGGER register to no avail. I've also experimented with changing the DAC SYNC EN bit and writing the LDAC bit after writing a new DAC CODE, all to no avail.

My 5V and 3.3V rails seem to come up in about 1mS.

I'm at a bit of a loss here and would appreciate any insights as to what might be going on with this chip. I don't see what my Vout should be anything but zero. The only response I seem to be getting from the chip with my i2c commands is when I set the REF_PWDWN bit in CONFIG, I see the VREFIO line go to zero. However when I set the DAC_PWDWN bit to 1, the output still 'stays stuck' and the voltages I mentioned above.

Thank you for your help.