- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Hello,

We are using the ADS9813 EVM along with the Zynq 7045 FPGA. The ADS9813 is mounted on the FMC of the FPGA. We plan to use the ADS9813 in a 4-lane SDR data rate configuration.

We have built and verified the logic for this setup in Vivado through simulation, and now we intend to implement it on hardware. However, we encountered some confusion regarding the initialization sequence in the ADS9813 datasheet. Our queries are as follows:

It would be helpful if you could provide the correct final initialization sequence for the ADS9813 and clarify the behavior of fCLK.

Best regards

Hi CT,

Thanks for your question. To better understand the use-case, could you please share what kind of an application you hope to use ADS9813 in?

I am awaiting confirmation from the team regarding the initialization sequence, let me get back to you on Monday. Are applying power and a free-running SMPL_CLK while trying to write the init sequence? FCLK malfunctioning may be a symptom of the device not being initialized properly, so we should resolve that first.

Best regards,

Samiha

Hello,

Any updates on the initialization sequence?

I also wanted to let you know that we are setting the SPI clock polarity and phase to zero, as per the timing diagram. Could you confirm if we are on the right track?

Best regards.

Hi CT,

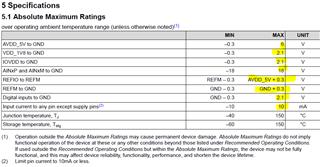

The confirmed sequence is as follows:

Yes, PHA and POL being 0 is correct for SPI.

Could you please share your schematic of the ADC so I may confirm all connections are correct? Also could you please go through these debug steps:

Best regards,

Samiha

Hello,

We are using the evaluation board itself, and we have measured the voltages with the following results:

After power-up, we are following the below sequence of register writes to initialize the ADS9813 and configure it for our use case:

0x0001 to register 0x00 (reset enabled).0x0000 to register 0x00 (reset disabled).0x0004 to register 0x00 (legacy SPI enabled).0x000B to register 0x04 (INIT1 configuration).0x0002 to register 0x03 (select bank 1).0x0002 to register 0x92 (INIT2 configuration).0x0604 to register 0xC5 (INIT3 configuration).0x0100 to register 0xC1 (set SDR data rate).We are using an SPI clock of 5 MHz with CPOL = 0 and CPHA = 0.

We are observing the data lanes (D0, D1, D2, D3) with respect to DCLK in the ILA and also monitoring FCLK in the ILA. The register initialization occurs based on our control logic.

Here is what we observed:

Before initialization:

D0, D1, D2, D3).FCLK is captured in the ILA (not periodic but detectable).After initialization:

D0, D1, D2, D3) and FCLK show zero in the ILA.We are providing an 8 MHz clock through the FMC to SAMPL_CLKP. We are using the default jumper configuration (no changes made to jumper positions).

Could you help us understand why we are not seeing any data or FCLK after initialization? Are we missing something in the initialization sequence? Have you encountered this issue?

Your assistance is greatly appreciated, as we are currently stuck at this point.

Best regards.

Hi CT,

Thanks for sharing. We recently fully released the ADS9813 so the production silicon is a little different compared to the preproduction silicon. Perhaps your EVM has preproduction silicon, depending on when you ordered it. Could you share what the marking on your ADS9813 device is? Is it ADS9813 or PADS9813? If it is PADS9813, it will be best to order a production device and replace the DUT on the EVM, as this may be causing the initialization sequence issues. The sequence in the datasheet is meant for production silicon.

Productiom silicon of ADS9813: https://www.ti.com/product/ADS9813/part-details/ADS9813RSHR

Best regards,

Samiha

Hello Samiha,

Thanks for your support. We have resolved the issue by creating a new project. We suspect a mismatch between the SDK and RTL, but we're not entirely sure. Now, we are able to perform initialization successfully. We tested with a custom pattern, which worked, and also verified it with an input signal.

We have a few queries:

Best regards

Hi CT,

That is good news! What kind of general application/project are you using ADS9813 for?

Regarding the noise, if plotting an FFT, depending on which input range, and bandwidth mode used, the SNR should be around 90.3dB. Front-end/system variables may introduce additional noise.

Yes, it looks like ramp output increments after every 16th sample:

Best regards,

Samiha

Hello samiha,

We are currently evaluating the performance of this ADC before finalizing it for our application.

Regarding the noise, the issue is not related to SFDR. We are observing a noise level of 50k—could this be the ADC's default noise swing?

Additionally, we have noticed that fclk is not aligning correctly with the data, even though sample_sync is provided. At times, the channel data appears to be circularly shifted, ( that is if we give input in channel 1 it is reflected in channel 2 or channel 3 sometimes).which we suspect is due to improper alignment between fclk and the data.

How can we resolve this issue?

Best regards

Hi CT,

What do you mean by 50k? Could you please clarify units or share a plot please? You could try shorting the positive and negative inputs of the ADC channel to see if the noise is internal to the ADC.

Are you providing SYNC pulse after power-up, with SMPL_CLK provided? Could you please provide a screenshot of oscilloscope or logic analyzer? SYNC must be provided anytime the SMPL_CLK frequency is also changed.

Best regards,

Samiha