Tool/software:

hello

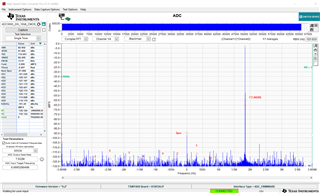

The following procedure is programmed from the ADC35XX EVM GUI.

I am not sure why ADC3660 is sometimes working correctly and sometimes not.

Please review if the procedure to ADC3660 is correct.

0x7 0x8

0x7 0x4B

0x13 0x1

0x13 0x0

0x1b 0x88

0x19 0x12

0x19 0x12

0x1f 0x50

0xa 0x7f

0xb 0xee

0xc 0xfc

0x18 0x10

0x20 0x0

0x21 0xf0

0x22 0xf

0x24 0x6

0x27 0x10

0x2e 0x10

0x7 0x4b

0x25 0x30

0x2a 0xa2

0x2b 0xa5

0x2c 0x43

0x2d 0xd4

0x31 0xa2

0x32 0xa5

0x33 0x43

0x34 0xd4

0x11 0x30

0x26 0x88

0x26 0xAA

0x26 0x88