Other Parts Discussed in Thread: ADC3683, TSW1418EVM, TSWDC155EVM

Tool/software:

Dear TI,

I am using:

- ADC35XX EVM GUI

- High Speed Data Converter Pro v6.00 (64Bit) (HSDC)

- TSW1418 EVM REV A

- ADC3683EVM (DC134, REV E)

to evaluate ADC3683.

Following ADC368xEVM User's Guide (sbau360.pdf), chapter 5 (Onboard Clocking Hardware Setup), I was able to modify ADC3683EVM board to use its internal clock circuitry (CDC) instead of the external clocks.

Using the above mentioned software and modified ADC eval board, I am able to operate the ADC in the bypass mode (i.e. without any downconversion and decimation) sucesfully without problems.

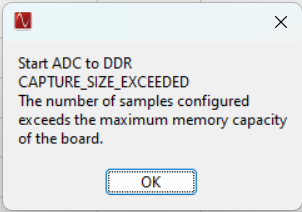

However, when I want to evaluate the ADC in its complex decimation mode while following the ADC368xEVM User's Guide, section 4.3 (Complex Decimation Mode) I get the following error in HSDC:

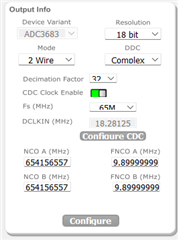

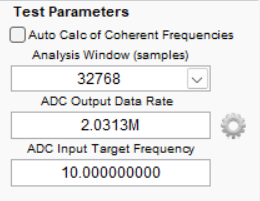

The settings of both sw tools look like follows:

Questions:

- Can you see any issue in the settings above?

- Would you have any idea what to try to make it working in this complex decimation mode?

- Following ADC368xEVM User's Guide, section 4.3.1, there is written that decimation factor 16 shall be used. But in section 4.3.2, there is written that decimation factor 32 shall be used. Is this intentional or is this a typo?

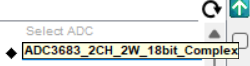

- Section 4.3.2 says that driver called „ADC3683_2W_18bit_Complex“ shall be used, however, in HSDC v6.00 I can find this particular one, so I am using ADC3683_2CH_2W_18bit_Complex. Is this alright? Or shall I use ADC3683_2CH_2W_18bit_Complex_s?

- In one of the setting above there is a field "ADC 2nd input frequency". What is this for? Please note that I want to operate ADC in the two channel mode (i.e. both channels provide samples in parallel simultaneously). Shall I be worried about this field somehow?

- Is there a possibility to evaluate the complex decimation mode with the 20bit output samples using the tools listed above? Currently it seems that only 18bit output is supported, but I might be wrong.

Note: I have not tried to evaluate the complex decimation mode with the external clocks at all... I simply started my experiments by switching to the internal clock.

Thank you very much!

Ondrej