Tool/software:

Hello everyone!

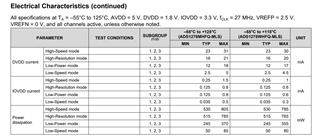

I have a doubt about the power consumption of the part at different clock frequencies. In the datsheet power consumption is detailed at a fclk of 27MHz. I plan on running the ADC at lower frequencies. Are there any data available about the power consumption vs fclk? Is there any formula I could apply?