Tool/software:

Hi Expert,

Could you please support below questions?

(1) From Figure 8-14 in the datasheet, the time from DRDY-Hi to tSETTLE3 is a waiting time, and after that, the ADC data can be converted with Sinc3 filter data = tDATA = 1/fDATA. Since this AFE has 6 ADC channels and simultaneous conversion is performed, please first confirm whether one Sinc3 filter data can obtain AD conversion data for all 6 channels, or whether six Sinc3 filter data for 6 channels are required. Table 8-8 states that AD conversion can be performed in 0.25 msec after waiting 0.823 msec, but this 0.250 msec AD conversion is a waiting time. Please let me know if it is okay to think that AD conversion can be performed in the same time of 0.25 msec many times after the 0.823 sec waiting time.

(2) Please also let us know the time of tGC_FIRST CONVERSION, tGC_CONVERSION, and tDATA below.

Please answer with OSR=1024, 512, and 256.

The conversion period of the first conversion after the ADC channels are reset is considerably longer than the conversion period of all subsequent conversions mentioned in Equation 8, because the device must first perform two fully settled internal conversions with the input polarity swapped. The conversion period for the first conversion in global-chop mode follows Equation 9.

tGC_CONVERSION = tGC_DLY + 3 × OSR x tMOD (8)

tGC_FIRST_CONVERSION = tGC_DLY + 3 × OSR x tMOD + tGC_DLY + 3 × OSR x tMOD + 44 x tMOD (9)

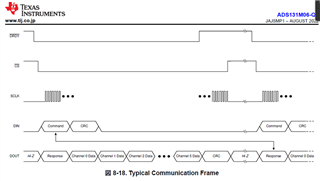

(3)The time of the SPI transmission data is calculated as follows, but please confirm that it is correct before answering. If it is different, please indicate the formula and the time.

fMOD=8.192MHz/2=4.096MHz

Response=16bit, Data for Channel 0-5=24bit, CRC=16bit

Total bits when sending all data from Channel 1-6 via SPI=16+24×6+16=176bit

Transmission time=176×(1/4.096*10^6)*10^-6=42.96875usec

Best Regards,

Yuki