Other Parts Discussed in Thread: DAC38J84, LMK04828

Tool/software:

Hi,

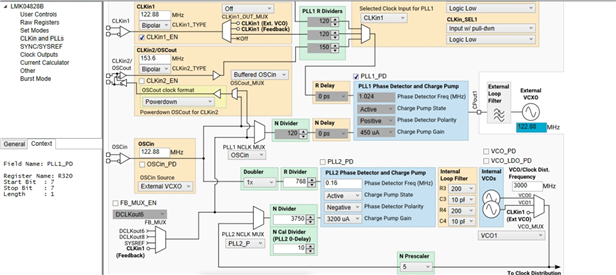

We are trying to generate the following clocks using Zero Delay Mode for Multi DAC Synchronisation ( using 2 DAC38J84 EVMs and Efinix Ti3775N1156 FPGA).

Device Clk = 125 MHz

DAC_Clk = 1000 MHz

PMA Clock = 100 MHz

Sysref = 3.90625 MHz. (Data Rate = 5 Gbps, Interpolation = x4).

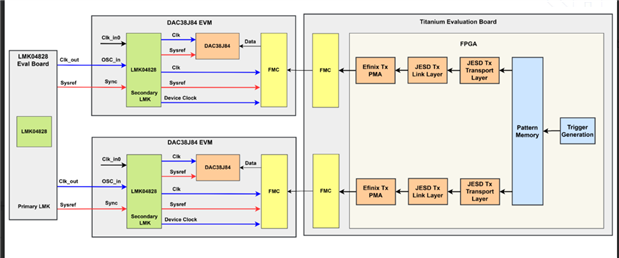

Primary LMK04828 will provide reference clocks to the secondary LMKs present on DAC EVMs as shown below.

So my question is:

1) Whether we are heading in the right direction concerning our clock configurations. Can we move with this setup for Multi Chip DAC Synchronisation ?

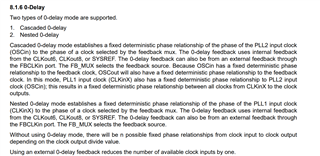

2) There are two variations of ZDM, Normal ZDM and Nested ZDM. Which one will be more suitable for our case?

Please let us know if any more info is needed. Recommendations for any improvements will be very helpful.