Tool/software:

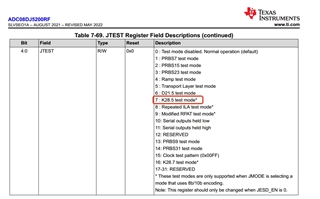

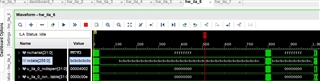

I use TI's ADC08DJ5200RF chip for data acquisition. Now I find that the sampled data is incorrect, so I use the built-in JTEST of the chip to conduct data testing from the ADC to the FPGA. When using K28.5, the data collected by the FPGA is unstable. What could be the possible reasons?