Other Parts Discussed in Thread: ADC3644EVM,

Tool/software:

Dear Technical Support Team,

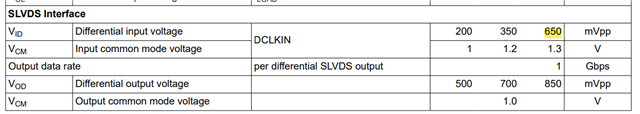

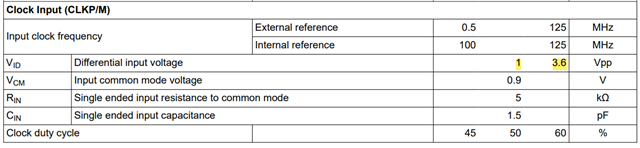

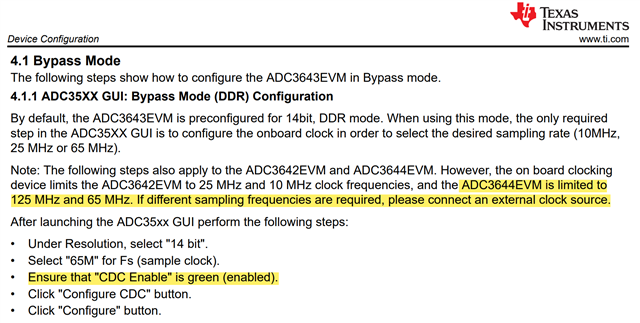

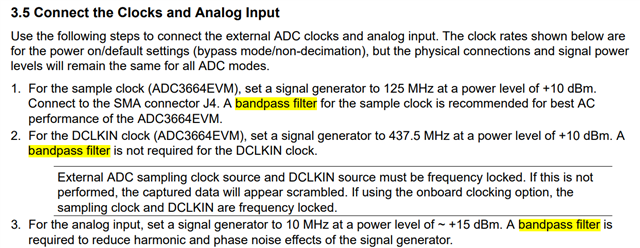

Accoriding to userguide, DCLK and Sampling clock input level should be +10dBm.

Which is correct to set sinewave(10dBm=2Vpp) or square wave(Vpp=1.414Vpp) from external pulse generator?

My function generator cannot set 437.5MHz square wave.

Userguide describes sampling clock and analog input is requre to get a good performace.

Does it mean signal generator setting? or implement it on the board circuits?

If you have any example, could you share it?

Best Regards,

ttd