Tool/software:

Hi team,

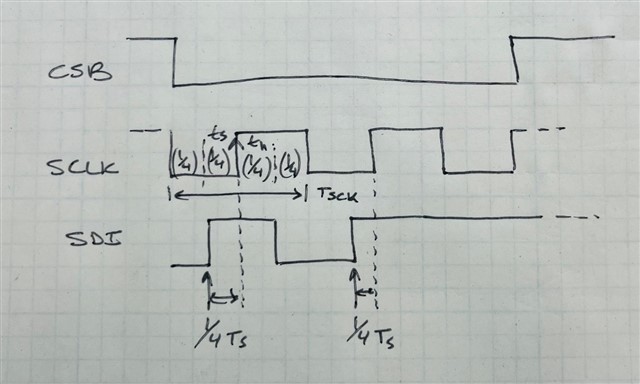

Our project uses xilinx Artix 7 FPGA interfaced with ADS5409 chip. Here, FPGA acts as the SPI master and ADC chip acts as the slave. We need to constraint the SPI interface using the below constraints

set_input_delay -clock clk_sck -max [expr $tco_max + $tdata_trace_delay_max + $tclk_trace_delay_max] [get_ports IO*_IO] -clock_fall;

set_input_delay -clock clk_sck -min [expr $tco_min + $tdata_trace_delay_min + $tclk_trace_delay_min] [get_ports IO*_IO] -clock_fall;

The min and max ( tco_min and tco_max ) values of the clock to output of SPI interface are not provided in the ADC datasheet. Could you please let us know what values have to assigned to tco_max and tco_ min ?

Thanks in advance.