Other Parts Discussed in Thread: ADC3644, ADC3643, , THS4541

Tool/software:

Dear Technical Support Team,

I installed HSDC v6.0, but it doesn't include ADC3644.

If I need to install patch, could you provide it?

Best Regards,

ttd

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Dear Technical Support Team,

I installed HSDC v6.0, but it doesn't include ADC3644.

If I need to install patch, could you provide it?

Best Regards,

ttd

Hi TTD,

Please see page 10 of the user guide. It says use the ADC3643 ini files.

Regards,

Rob

Hi Rob,

Thank you for you reply.

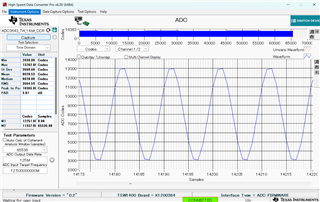

I tried ADC3643 ini files on HSDC pro. it seems to be sampling input analog data.

My target sampling rate is 125MSPS with ADC3644EVM, so I set 125MHz with "CDC Enable" on ADC35XX GUI.

Does it work correctly?

Best Regards,

ttd

Hi TTD,

Please let me know what data capture board and setup you are using.

Regards,

Rob

Hi Rob,

Thank you for your reply.

My configuration is ADC3644EVM(ADC35XX GUI) + TSW1400EVM(HSDC Pro v6.0).

Anaglo input is 12.5MHz and Sampling Clock is 125M, so I got sine wave(1cycle) with 10 samples.

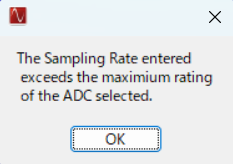

I ignored following message when I set 125M for "ADC Output Data Rate" on HSDC pro, because using ADC3643 ini files.

Q1:

What is the max analog input range(dBm、Vpp) for J1?

ADC3644EVM has THS4541 intsted of transfomer before ADC input.

Q2:

If my evaluation for 125M is correct, I'd like to change 100MSPS.

According to the userguide, it is required to use external clock(If CDC generate 100M, it's the best solution, but it doesn't support on GUI(CDC Disable)).

Then my understanding , I need to try change hardware for 100MSPS based on "5 External Clocking Hardware Setup"

Is it correct?

• DNI R32, R40 ⇒ Disable InternalCLK from CDC

• Install R36, R37 (0-Ω resistor) ⇒Enable external Clock from J8

• Connect sample clock to J8. Connect DCLKIN to J15.

• DNI R176 ⇒ Disable InternalDCLKIN_P

• Replace C129 with 0-Ω resistor

Best Reagrds,

ttd

Hi TTD,

When using the THS in front of the ADC. I would start at -10dBm and walk it up.

It really depends on the configuration of the amplifier, filter, etc.

From the codes output you are showing above, you are not clipping.

On the external clock changes. Please send me a picture of your EVM. We have had a few revisions and I want to make sure which changes to guide you with.

In general, I would not use the CDC, it supports only a limited number of sampling rates.

Regards,

Rob

Hi Rob,

Thank you for your reply.

I started the small level and up to 1Vpp(3.979 dBm) during checking not clipping on GUI code.

Here is the pictures I attached. I believe this is the rev.F(DC104F).

I inserted my comment to the schematic and picutres for external sampling clock from SMA(J8).

It seeems no to change C and R around SMA(J13) of DCLKIN due to DDR CMOS mode(Not CMOS serialized mode).

Could you review it?

I have been referinig the schematic on following E2E attached.

e2e.ti.com/.../OutputFiles.zip

Best Regards,

ttd

Hi TTD,

The PPT mods look correct to me.

Is everything working?

Regards,

Rob

Hi Rob,

Thank you for reviewing my ppt.

I haven't tried to rework it, but I understand that my ppt seems to be correct on your check.

Best Regards,

ttd