Other Parts Discussed in Thread: ADS1278, ADS1278-SP, MSP430FR5969

Tool/software:

Hello everyone,

I am using the ADS1278EVM-PDK evaluation board to prototype a data subsystem for the ADS1278-SP ADC chip. For our data system, we plan to interface the ADS1278 chip with an FPGA board using the frame-sync protocol, as this approach provides a deterministic state machine—especially important since I intend to switch the external analog input after each sample.

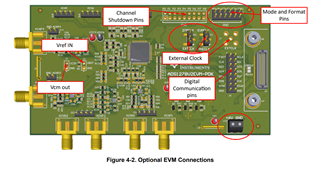

Initially, I controlled the EVM through the PHI controller using the ADS1278 GUI and captured signals (DOUT1, SCLK, FSYNC, CLK) with an oscilloscope to verify timing diagrams and confirm my understanding based on the datasheet.

Next, I plan to interface the EVM using my own FPGA design without the PHI controller. Before proceeding further, I would greatly appreciate feedback from TI engineers and the community regarding my hardware and configuration setup outlined below.

Hardware System:

Due to limited available I/O, I will use only one of the eight channels. An external analog multiplexer (MUX) will eventually switch the input signal. Currently, I'm using a stable 1.5 V DC signal for initial testing.

1. Disconnect the PHI controller connector from the EVM.

2. Solder pin headers onto the unused PWDN pins and use jumpers to disable unused channels (the corresponding PCB holes are unpopulated).

3. Tie the configuration pins to GND or 3.3 V as specified by my intended configuration.

4. Select EVMCLK using the onboard oscillator OSC_Y1

5. Use the EVM's provided 6 V supply connector for power.

Configuration:

-

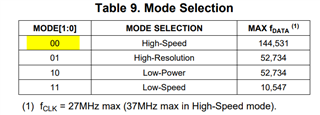

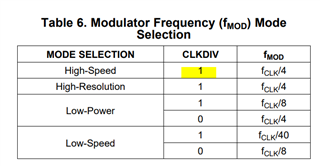

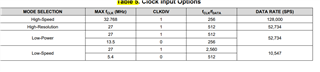

Mode: High-Speed (using the onboard 27 MHz oscillator initially; we may maximize Fclk later if needed).

-

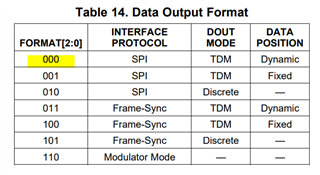

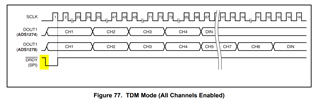

Frame-Sync, TDM, Dynamic mode (PWDN = 1 for the active channel, 0 for unused channels).

-

CLK_DIV set to 1.

-

Test mode disabled.

I/O

-

SYNC: Synchronization (initial reset)

-

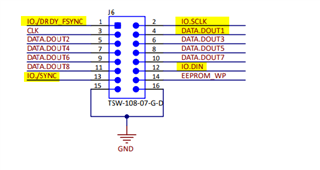

FSYNC, DOUT1, CLK, SCLK for Frame-Sync communication

-

CLK to SCLK ratio = 1

FPGA logic:

1. Pull SYNC low for at least one CLK cycle (currently using two cycles).

2. Generate 128 FSYNC periods (each FSYNC period consists of 256 CLK cycles, 50% duty cycle) to prepare data conversion.

3. Start reading data at the beginning of the next FSYNC cycle. Sample data on the rising edge of SCLK since data shifts out on the falling edge.

**Question:

-

Does my hardware and FPGA setup appear correct?

-

What is the recommended power sequencing between the FPGA board and the ADS1278EVM-PDK? Should the FPGA board power on first, or vice versa? If the FPGA must be powered first, I'll add logic to prevent automatic FSM startup.

-

Must I assert the SYNC signal and then wait another 128 FSYNC cycles every time I switch the analog input after each sample? I must switch the input signal as all input signals represent different science data.

-

Is an FPGA necessary for interfacing with the ADS1278-SP chip, or can an MCU such as the TI MSP430FR5969 achieve the same performance? Given the limited pins on the mission main processor, any recommendations for alternative interfacing methods would be welcome.

Thank you in advance for your guidance and feedback!