Tool/software:

Hi, I am having problems modifying the gain setting registers on the ADS131M02. The ADC works on default settings as I have successful communication via SPI with a raspberrypi 5, but the problem arises when I try to change the gain of one or both channels to something else than 1.

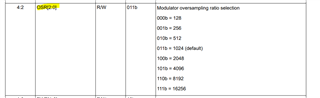

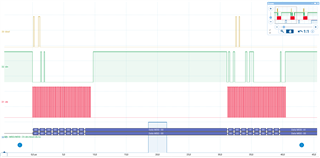

Looking at the SPI MOSI line (RPI out ADC in) on an oscilloscope the command seems correct. I built the command using the datasheet WREG command and the GAIN register on address 4, getting 32 bits:0110 0010 0000 0000 0010 0010 0000 0000 --- 011 being the WREG command, 000100 being address 4, 0000000 being 1 register to write and then the 16 bits of register settings, setting both channel gains to 2. When sending this command I receive back a correct response with the address and registers written. The ADC does not change the amplitude of the output data though (the test sin wave stays the same).

Does anyone have any ideas what could be the problem?