Tool/software:

TI-ADS1261 ADC is always transmitting bytes with a value of zero over SPI bus back to master.

TI-ADS1261 Analog to Digital Converter is connected to Xilinx Zynq 7020 SOC (System On a Chip) through the Zynq SPI Bus Serial Interface. Pins used for communication are CS (Chip Select), SCLK (Serial Clock), DIN (Data Input) and (DOUT/DRDY) Data Output / Data Ready. SLCK is running at 33 MHz / 512 = 65.104 KHz with a period of 15.36 Microseconds.

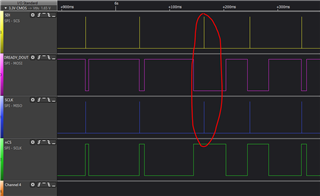

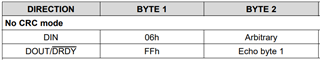

The correct number of bytes is transmitted by the ADS1261 in response to commands and read registers but the value of all bytes is zero. For instance sending a reset command - 0x06, 0x00, 1261 responds with 0x00, 0x00 instead of 0xFF, 0x06. Or sending RREG of Status Register = 0x21, 0x00 1261 responds with 0x00, 0x00, 0x00 instead of 0xFF, 0x21, <Status Register Value>.

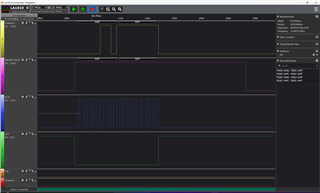

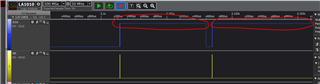

My hardware engineer placed a scope on the SCLK, DIN and DOUT. Clock looks good, DIN is being correctly driven by Zynq SPI and DOUT is being driven by 1261 with bytes that are serial zero for every byte.

Our software is initializing as follows.

Reset SPI, First initialize the SPI Bus system clock, interrupts, configuration register, Reset SPI. as follows:

Xilinx SPI Configuration Register CR = 0x0000FC35

// Bit 17 = 0 ModeFail Generation Disable

// Bit 16 = 0 Manual Start Command

// Bit 15 = 1 Manual Start Enable

// Bit 14 = 1 Manual Chip Select Mode

// Bit 13:10 = 1111 No Slave Selected

// Bit 9 = 0 Peripheral Select decode Only 1 0f 3 selects

// Bit 8 = 0 Use SPI Reference Clock

// Bit 7:6 = 0 Reserved

// Bit 5:3 = 110 Baud Rate Divisor Divide by 128

// Bit 2 = 1 Clock phase SPI clock is inactive outside the word

// Bit 1 = 0 Clock Polarity outside SPI word SPI Clock is quiescent low

// bit 0 = 1 Mode Select SPI is in Master Mode

Then we use the initialized SPI bus to initialize the TI-ADS-1261 as follows:

Send command reset, read status register, write all registers with default values.

TI-ADS-1261 responds to reset command and all write register commands with all zeros.

We are using the TI-ADS-1261 as our ADC for reading various critical voltages in real-time from our hardware.

Any help in getting the TI-ADS-1261 up and running, much appreciated.