Other Parts Discussed in Thread: , AM5728

Tool/software:

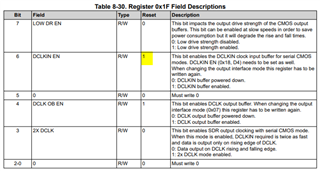

Using the same register settings, simply changing the DCLKIN frequency from 12MHz to 40.96MHz causes the data being read to change from a count of about 11000 to a count of about 12000. We are feeding a DC voltage for testing purposes.