Other Parts Discussed in Thread: ADS1278

Tool/software:

Hello everyone,

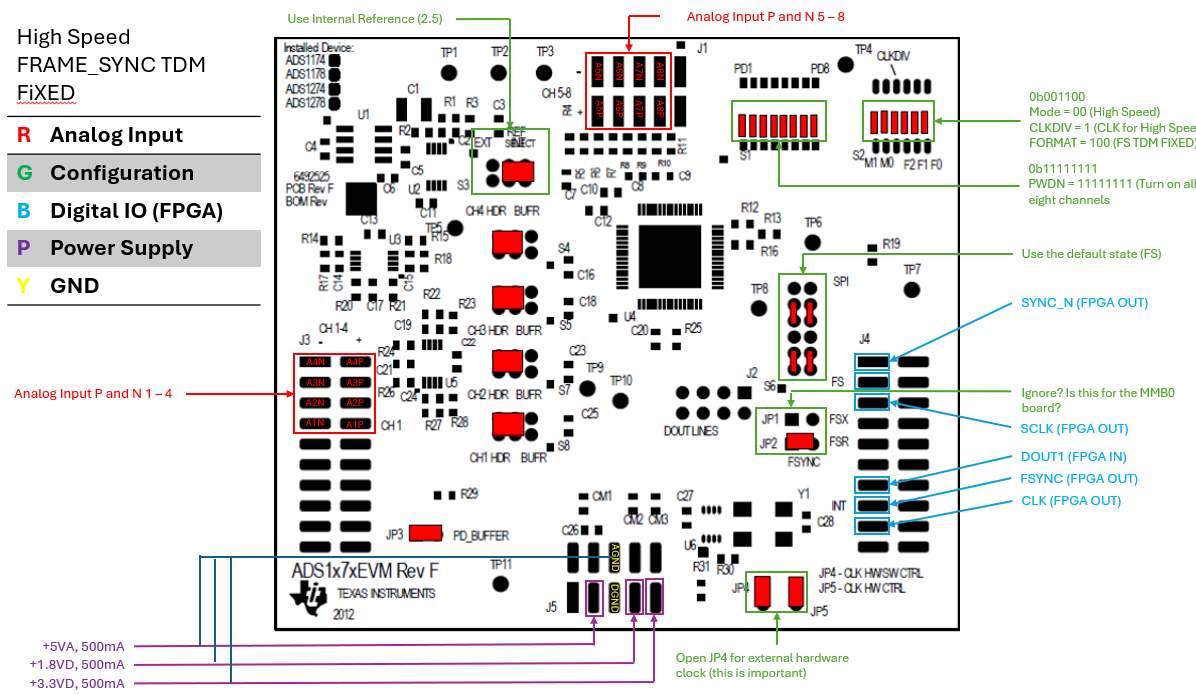

We are using an older ads1278 EVM to prototype our system and have set up the power supply as follows:

- Power Sources: Two separate dual-channel DC power supplies providing 5V, 3.3V, and 1.8V, each set to 0.5A limit

- Issue: The board does not power on standalone (unable to receive ADC data using an FPGA system that worked the lastest ads1278 EVM).

- Current Observation: When all three power supplies were turned on, the 5V and 3.3V channels drew only ~0.01A, and the 1.8 channel drew no current.

- ADS1278EVM-PDK Evaluation Module V1.pdf

I have a few questions regarding proper power-up:

- Does this EVM have a Power Good indicator or test point to check the status of the power rails?

- Is there a required power-up sequence for 5V, 3.3V, and 1.8V?

- I connected the grounds of all three power supplies together and tied them to AGND on J5 Pin 6 (top row, middle). Is this the correct approach?

Any guidance on these issues would be greatly appreciated.

Thank you!