Other Parts Discussed in Thread: ADC14X250

Tool/software:

Hi,

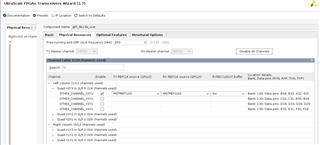

my project connects a ZCU102 with an ADC14X250 EVM. After configuring the IP to match the ADC features (8b10b, 1 Rx lane, 5 Gbps lane rate, etc.), the next step is to develop the application layer. For that the plan was to connect the Tx and Rx ends of the TI-JESD204 IP in loopback in simulation together with the application logic.

However I am running into issues running the TI-JESD204 IP Questa simulation model. However, both cpll and qpll outputs always remain in high impedance ('Z'). I tried adding the simulation libraries for the Xilinx GTH transceivers to my Questa environment but that did not help either.

Some information about my simulation setup:

- mgt_freerun_clk runs at 100MHz

- mgt_refclk_p/n run at 156.25MHz (same as in the zcu102 8b10b reference design)

- Both sys clocks run at 156.25MHz (same as in the zcu102 8b10b reference design)

- master_reset_n held low for 200ns, then high

- Simulation runtime 200us

Is this QuestaSim simulation workflow fully supported or does it have limitations?

Thanks

--

Mariano Maté